Part Number: ADC12DJ3200

Other Parts Discussed in Thread: LMK04828,

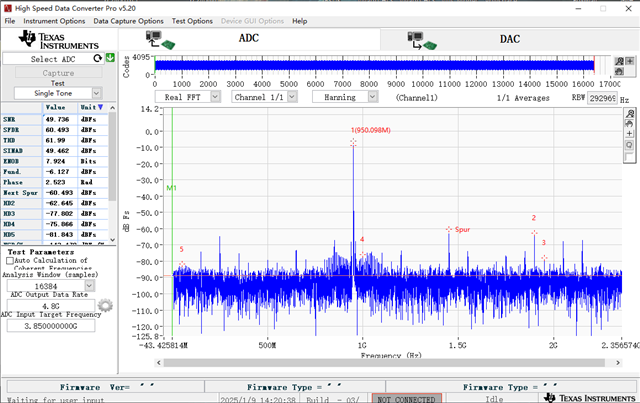

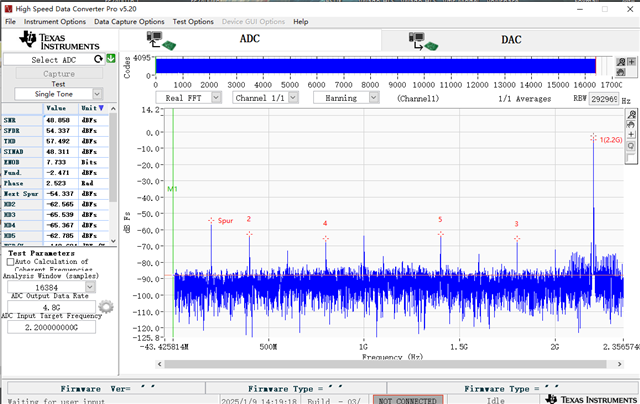

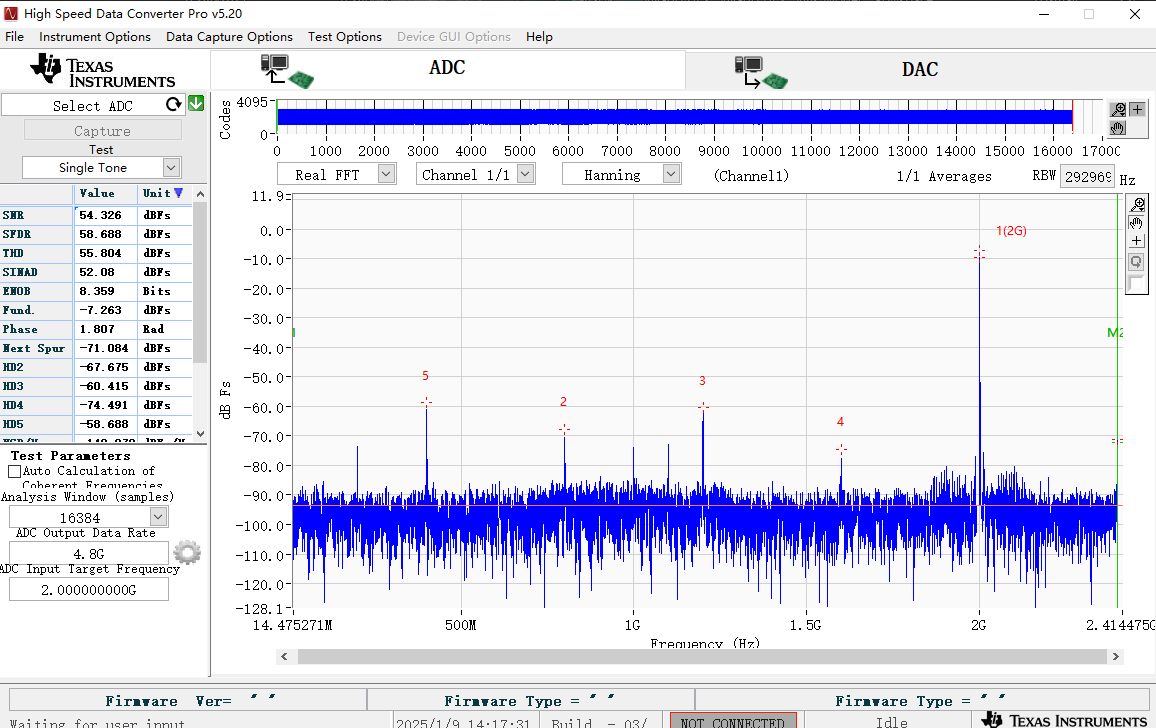

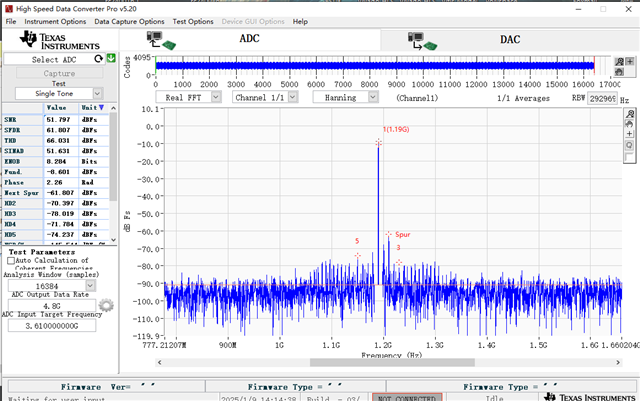

使用jmode0模式,采样率4.8G,采集2.6~4.6G的信号,出现如下所示的杂散。

需要进行那些校正才可以较小这些杂散呢,;

以下是我的配置,我已经进行了sysref的校准,在启动CAL_SOFT_TRIG = 1校准之前。

// 1. 启动或重置设备。

adc_cfg_rom[00] = 32'h000000B0;

adc_cfg_rom[01] = 32'h00000030; //软复位

adc_cfg_rom[02] = 32'h00000030; //软复位

//3. 编程 JESD_EN = 0 以停止 JESD204B 状态机并允许设置更改。

adc_cfg_rom[03] = 32'h00020000;

//4. 编程 CAL_EN = 0 以停止校准状态机并允许设置更改。

adc_cfg_rom[04] = 32'h00006100;

// 5. 编程所需的 JMODE。

adc_cfg_rom[05] = 32'h00020100; // Set JMODE0

// 6. 编程所需的 KM1 值。KM1 = K–1。

adc_cfg_rom[06] = 32'h0002021F; //设置 k =32

// 7. 根据需要编程 SYNC_SEL。选择 SYNCSE 或时间戳差分输入。

adc_cfg_rom[07] = 32'h00020402;

adc_cfg_rom[08] = 32'h000030ff;

adc_cfg_rom[09] = 32'h000031ff;

//These bits enable adjustment of the analog full-scale range for INA±.

// 8. 根据需要配置设备校准设置。根据需要选择前台或后台校准模式和偏移校准。//0x062默认进行前台校准

adc_cfg_rom[10] = 32'h00006205; //01 or 05//Calibration Configuration 0 Register(CAL_CFG0)

adc_cfg_rom[11] = 32'h0020900;//

adc_cfg_rom[12] = 32'h00080bc;// TADJ_A_FG90。

// 9. 编程 CAL_EN = 1 以启用校准状态机。

adc_cfg_rom[13] = 32'h00006101;// Set CAL_EN (always before JESD_EN)

// 10. 通过 OVR_EN 启用超范围并根据需要调整设置。OVR_EN

adc_cfg_rom[14] = 32'h0002130f; //[3] Enable overrange, [2:0]set overrange holdoff to max period 8*2^7 = 1024 samples

adc_cfg_rom[15] = 32'h00004803; //03 Set serializer pre-emphasis to 3

// 11. sysref 校准。

adc_cfg_rom[16] = 32'h00002930; //[5] 启用 SYSREF 接收器电路 SYSREF_RECV_EN=1 ,SYSREF_ZOOM =1,SYSREF_SEL 设置为 0

adc_cfg_rom[17] = 32'h00002970; //[6] 启用 SYSREF 处理器 SYSREF_PROC_EN=1。必须设置此位以允许设备处理 SYSREF 事件

adc_cfg_rom[18] = 32'h00002A04; //

// 12. 编程 JESD_EN = 1 以重新启动 JESD204B 状态机并允许链路重新启动。

adc_cfg_rom[19] = 32'h00020001;// Set JESD_EN (always after CAL_EN)

// 13.加载或启用 FPGA JESD204B 链路固件(输出解除204Bip复位的信号)

adc_cfg_rom[20] = 32'h00020001;//延时

adc_cfg_rom[21] = 32'h00020001;//延时

// 14.对 CAL_SOFT_TRIG=0进行编程、以暂停器件性能校准过程

adc_cfg_rom[22] = 32'h00006C00;// Set CAL_SOFT_TRIG low to reset calibration state machine

// 15.编程 SRC_EN=1来启动 SYSREF 校准过程

//********** 进行 SYSREF 自动 校准 ************* 需要连续sysyref

//如果 SYSREF 周期超过支持的值,则校准失败。

adc_cfg_rom[23] = 32'h0002B105; //0X2B1 SYSREF Calibration Configuration Register //Program SRC_CFG before setting SRC_EN

adc_cfg_rom[24] = 32'h0002B001; //0X2B0 SYSREF Calibration Enable Register //确保在设置 SRC_EN 之前 ADC 校准当前未运行。

//可以监控 SYSREF 校准状态寄存器中的 SRC_DONE( 0x2B2 [17]),以确保 SYSREF 校准已完成

//自动 SYSREF 校准完成后,可以执行其余启动过程以完成系统启动。

adc_cfg_rom[25] = 32'h0002B001; //延时

adc_cfg_rom[26] = 32'h0002B001; //延时

// 16.反复读取 SRC_DONE 位( 0x2B4 0x2B3 0x2B2 的 [17] 相当于0x2B4 [1] )以确认 SYSREF 校准过程已完成。

adc_cfg_rom[27] = 32'h0082B200;

//监控 SYSREF 校准状态寄存器中的 SRC_DONE( 0x2B4 0x2B3 0x2B2 [17]),

//以确保 SYSREF 校准已完成,SRC_TAD ( 0x2B4 0x2B3 0x2B2 [16:0])读取自动 SYSREF 校准发现的 tAD 调整设置。

adc_cfg_rom[28] = 32'h0082B300;

//监控 SYSREF 校准状态寄存器中的 SRC_DONE( 0x2B4 0x2B3 0x2B2 [17]),

//以确保 SYSREF 校准已完成,SRC_TAD ( 0x2B4 0x2B3 0x2B2 [16:0])读取自动 SYSREF 校准发现的 tAD 调整设置。

adc_cfg_rom[29] = 32'h0082B400;

//监控 SYSREF 校准状态寄存器中的 SRC_DONE( 0x2B4 0x2B3 0x2B2 [17]),

//以确保 SYSREF 校准已完成,SRC_TAD ( 0x2B4 0x2B3 0x2B2 [16:0])读取自动 SYSREF 校准发现的 tAD 调整设置。

adc_cfg_rom[30] = 32'h0082B400;

//监控 SYSREF 校准状态寄存器中的 SRC_DONE( 0x2B4 0x2B3 0x2B2 [17]),

//以确保 SYSREF 校准已完成,SRC_TAD ( 0x2B4 0x2B3 0x2B2 [16:0])读取自动 SYSREF 校准发现的 tAD 调整设置。

adc_cfg_rom[31] = 32'h0082B400;

//监控 SYSREF 校准状态寄存器中的 SRC_DONE( 0x2B4 0x2B3 0x2B2 [17]),

//以确保 SYSREF 校准已完成,SRC_TAD ( 0x2B4 0x2B3 0x2B2 [16:0])读取自动 SYSREF 校准发现的 tAD 调整设置。

// 17. 编程 CAL_SOFT_TRIG = 1 以启动校准。

adc_cfg_rom[32] = 32'h00006C00;// Set CAL_SOFT_TRIG high to enable calibration

adc_cfg_rom[33] = 32'h00006C01;// Set CAL_SOFT_TRIG high to enable calibration