Part Number: ADS1284

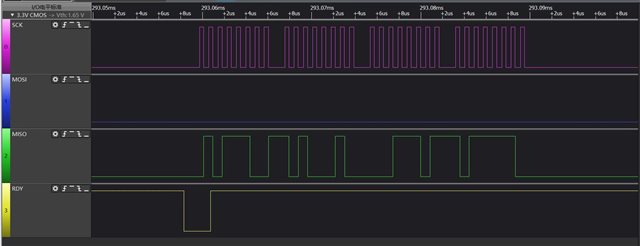

TI的技术专家们好,我在初步调试ADS1284的过程中,发现DRDY信号并没有在时钟的第一个下降沿拉高,这不符合datasheet中关于DRDY信号的描述。请问这是怎么回事,对我的应用有影响吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

这个波形是初始上电测得的,还是工作中测得的?

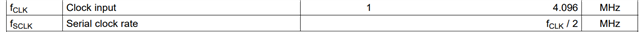

fsclk是1MHZ?

DRDY复位为高,用于指示芯片处于转换状态。

ADS1284 High-Resolution, Analog-to-Digital Converter datasheet (Rev. A)