Part Number: ADS4249

选择ADS4249为CMOS输出模式,输入时钟为100MHz,供电1.8V正常,RESET上拉到高电平,SCLK、SEN、CTRL1、CTRL2、CTRL3均配置为低电平。在测试随路时钟输出时发现频率正常为100MHz,但是峰峰值只有900多mV,这是怎么回事呢?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADS4249

选择ADS4249为CMOS输出模式,输入时钟为100MHz,供电1.8V正常,RESET上拉到高电平,SCLK、SEN、CTRL1、CTRL2、CTRL3均配置为低电平。在测试随路时钟输出时发现频率正常为100MHz,但是峰峰值只有900多mV,这是怎么回事呢?

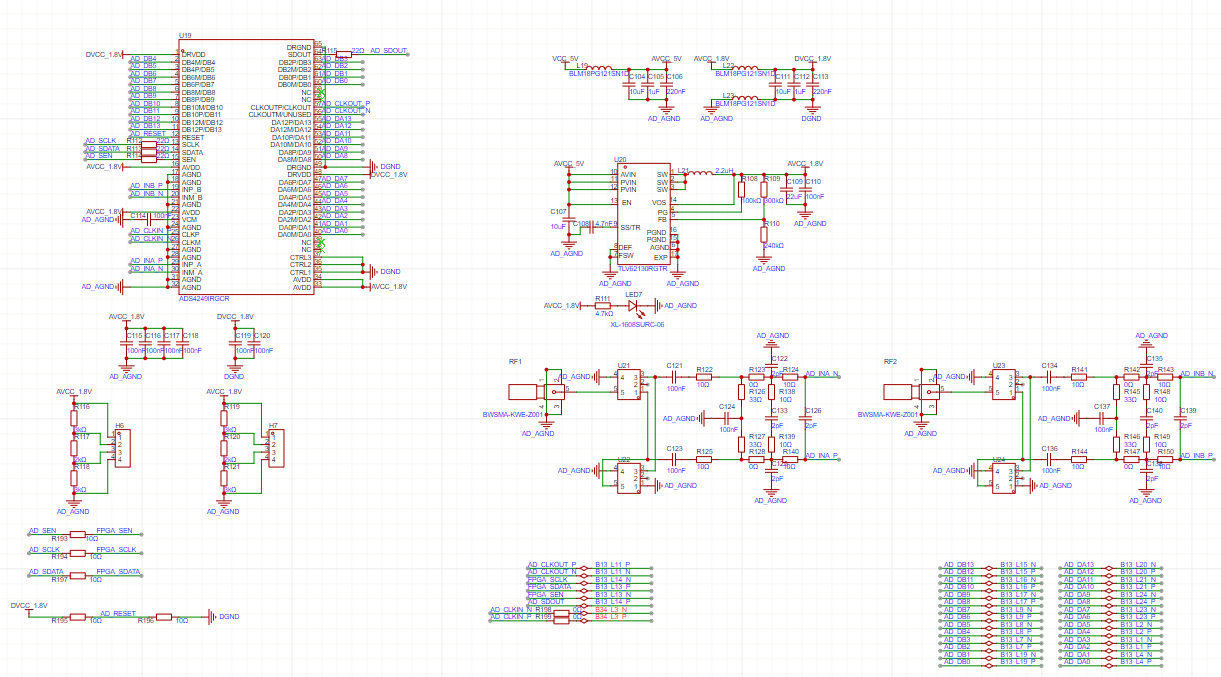

您好,这是ADS4249部分的原理图,随路时钟那里在原理图中是差分线,但是在PCB中是按照单端信号布线的

您好,这是ADS4249部分的原理图,随路时钟那里在原理图中是差分线,但是在PCB中是按照单端信号布线的

在上面的示波器捕捉中,你探测的是什么输出?MSB,LSB?在ADC输出的位中间的某个位置?

输出位是如何连接的?这在示意图中没有显示吗?FPGA?它们之间有电路吗?距离是多少?

请提供这些细节和/或图片。

其他输出看起来正常吗?

clkout是如何终止的?此连接是否通过连接器?它是否连接到FPGA?

你能分享一个示意图吗?

同样,我们需要更多关于这是如何联系起来的细节,以便我们提供更好的指导,因为你不应该看到这种行为。