Part Number: LMP92066

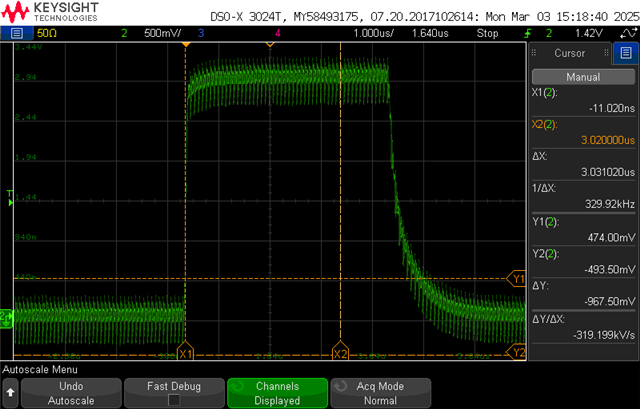

LPMS92066PWPR输出波形存在下拉较慢的情况

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

是从FETDRV引脚还是DAC引脚进行测试? 它看起来像一个电容放电图。 降低FETDRV引脚上的电容负载将有助于提高接通和关闭性能。

将此容量降低到100pF或10pF将使地面摆动多路器更短。 因此,较低的容量将减少振荡,因此您需要找出速度和可靠性的首选组合。 与电容器串联添加一个小的(~100OM)电阻器也有助于提高容量。