Part Number: DAC7821

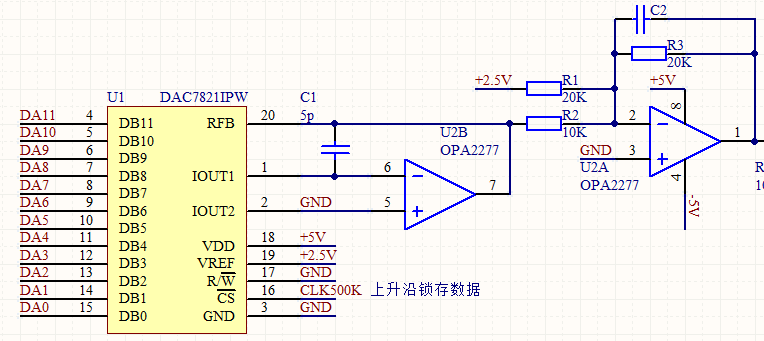

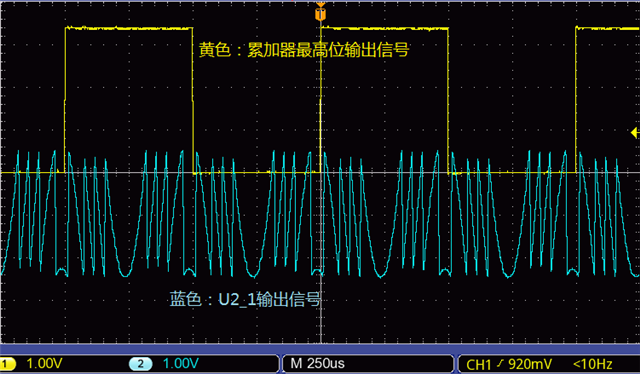

用赛灵思的ZYNQ系列设计DDS信号,DDS的时钟频率是500khz,累加器的最高位能够输出1000Hz的方波。取累加器高12位作为正弦波的地址信号,正弦波数据信号发给DAC7821。参考DAC7821手册电路设计如下左图,U2_1为何输出如下右图所示的波形?7821的CS信号是上升沿锁存数据,考虑数据稳定,将CLK500K取反给7821也试过,差不多。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

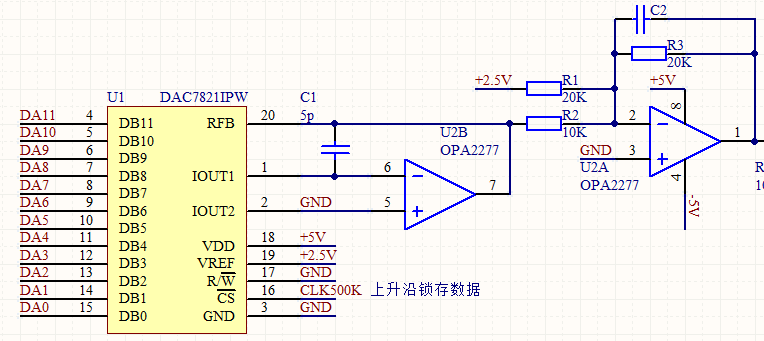

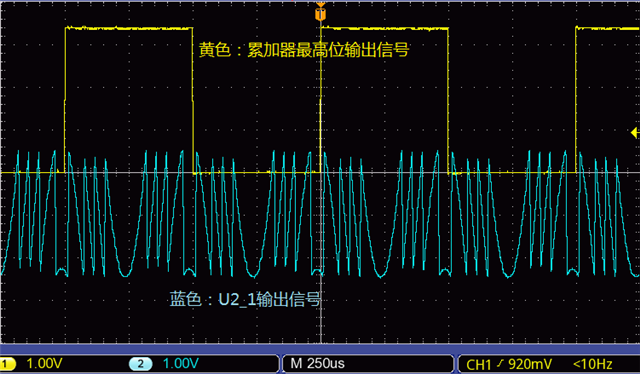

Part Number: DAC7821

用赛灵思的ZYNQ系列设计DDS信号,DDS的时钟频率是500khz,累加器的最高位能够输出1000Hz的方波。取累加器高12位作为正弦波的地址信号,正弦波数据信号发给DAC7821。参考DAC7821手册电路设计如下左图,U2_1为何输出如下右图所示的波形?7821的CS信号是上升沿锁存数据,考虑数据稳定,将CLK500K取反给7821也试过,差不多。