Part Number: ADS41B49

各位好:

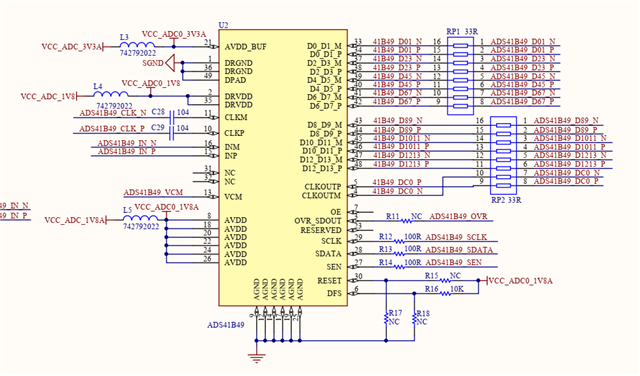

在我们自己设计的采集板上,使用了zynq 7z100和ads41b49,其中zynq 7z100位于核心板上,adc41b49位于底板上,核心板与底板之间通过连接器对插。ADC采样率为166MHz,FPGA与ADC之间使用LVDS接口,FPGA使用的是ADC提供的随路时钟对并行数据进行采样。

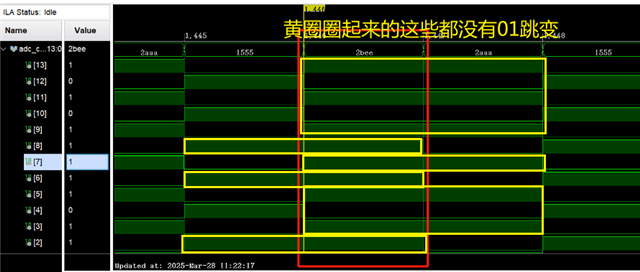

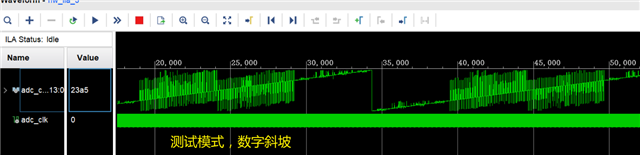

目前我们遇到的问题是FPGA采到的数据总是有毛刺,无论是真实输入的正弦波信号,亦或是测试模式下的0101序列,或者测试模式下数字斜坡,都能看到毛刺。如下图。

1. 尝试利用FPGA的IDELAY来单独调整时钟延迟,或者单独调整每一个数据脚的延迟,毛刺依然存在。

2. 尝试降低采样率,由166MHz降低到25MHz,毛刺依然存在。

3. 尝试使用CMOS并行接口模式,毛刺依然存在。

4. 尝试更换FPGA核心板,以及ADC采集底板,毛刺依然存在。

5. 检查过硬件设计,电压,参考时钟,没有发现明显异常。

——我很困惑。

在问题得到解决之前,我没办法确定到底是电路设计有问题,还是FPGA接口程序问题。希望你们能提供一些建议或者思路,谢谢。

下面是ADC部分的原理图(希望有用):