Part Number: DAC70508

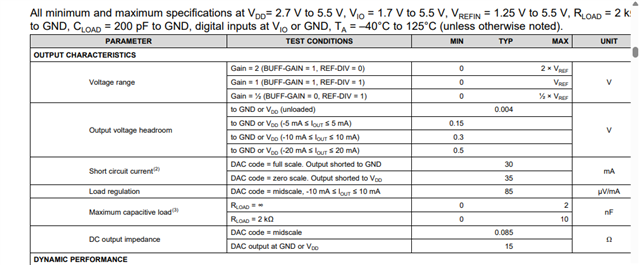

如下图,手册规定了两种情况下的容性负载,在负载无穷大的情况下容性负载最大为2nF,通常对于DAC输出直接接入运放的同相输入端时,允许的最大电容为2nF;这样理解对吗?另一种是在2K的负载下,容性负载最大为10nF,这是否意味着,若我在DAC的输出端加入一个低通滤波,再接入运放的同相输入端时,若电阻选择的是2K,那么最大电容为10nF,那么要想降低低通滤波的截止频率只能增大电阻,那么增大电阻后所能带的最大电容又是多少呢?是这样的意思吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

请您参考以下原图显示,这两个是测试条件。官方在相关条件下做的测试后给出的参考范围。

,那么要想降低低通滤波的截止频率只能增大电阻,那么增大电阻后所能带的最大电容又是多少呢?

至于您这个问题,建议使用以下两种方式来进行评估

https://www.ti.com.cn/cn/lit/zip/slam325

官方的仿真模型将您的设计导入进行仿真来评估

https://www.ti.com.cn/tool/cn/ANALOG-ENGINEER-CALC

官方给出的计算工具,您可以通过这个工具及进行理论评估。