DLPLCRC410EVM(DLP® Discovery™ 4100 )开发板和 DLP7000 DMD器件进行灰度图像显示时,有时显示不正常。通过Chipscope抓波形后看到:

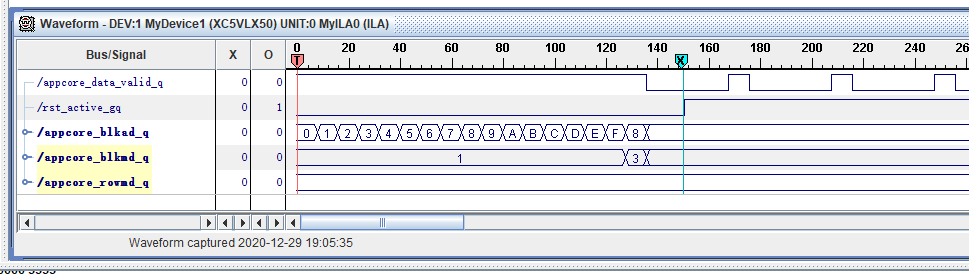

claer指令时序:

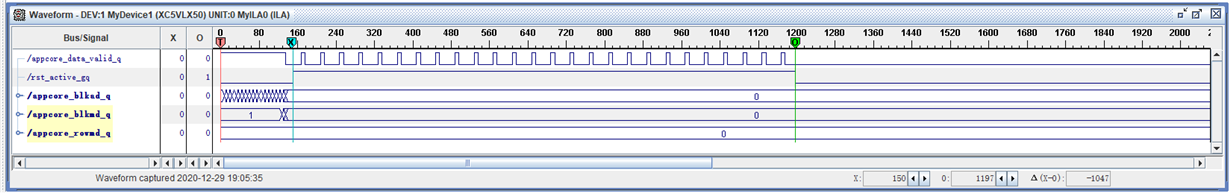

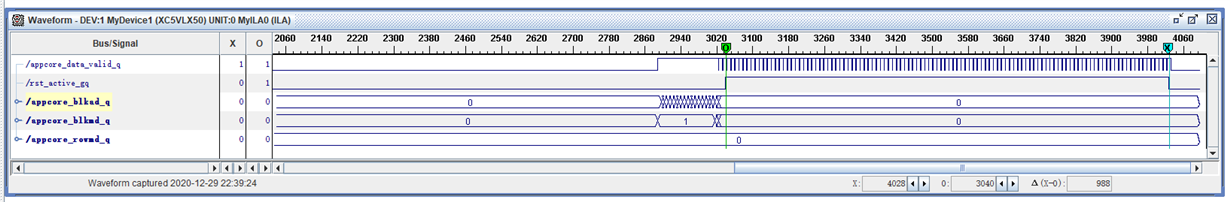

显示正常时时序:

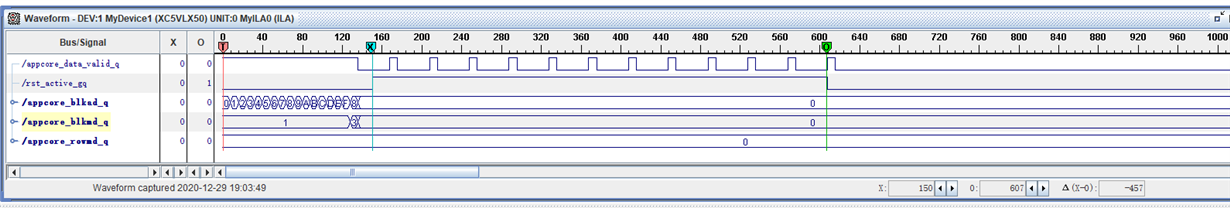

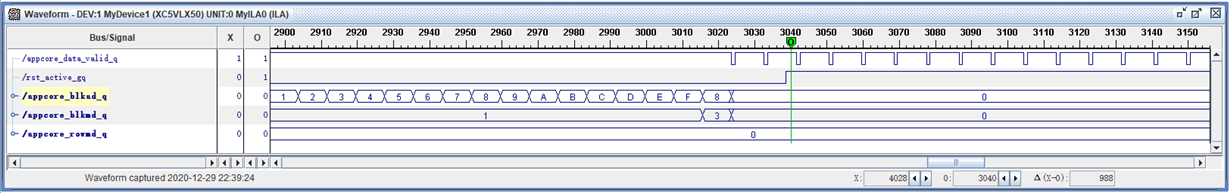

显示不正常时时序:

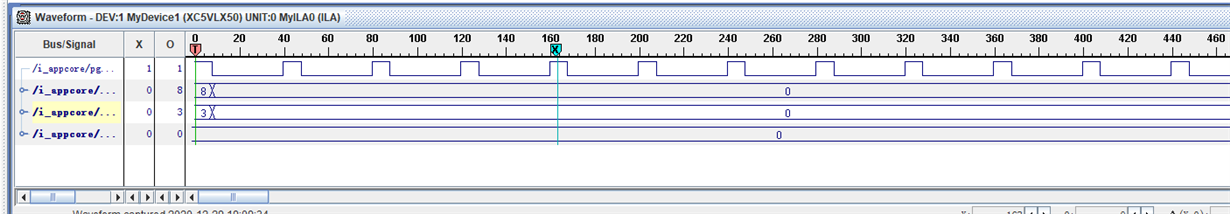

下面这个是抓到的Ti的dome里的复位时序:

显示正常时rst_active拉高了5.235us,显示不正常时rst_active只拉高了2.375us,都与手册描述不符合。想请问复位时时序到底应该是什么样的?为什么使用clear时使用同样的时序有时可以复位成功有时又不可以?