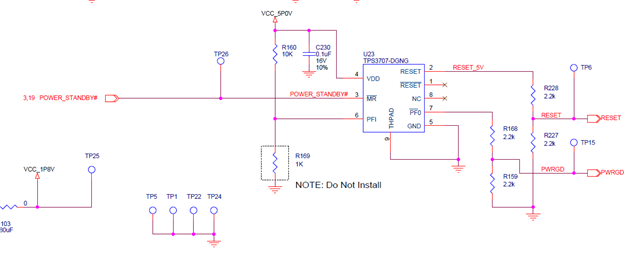

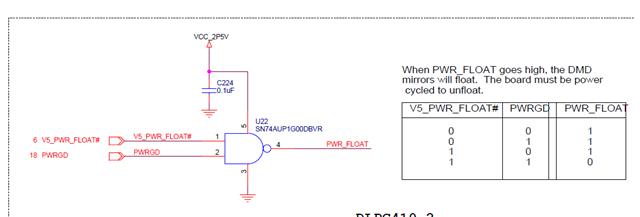

你好,使用自己设计的PCB在调试中发现,使能PWR_FLOAT现象出错,现象是在DMD上留下一个若隐若现的图像,该图像为使能PWR_FLOAT之前DMD显示的图像,能肉眼看到微镜并没有放平。

在英文论坛与TI工程师交流如下。

目前的主要现象是,①通过下电的方式使能PWR_FLOAT,“残影”存在,但在下电后约2-3s消失;②通过FPGA逻辑使能PWR_FLOAT,“残影”持续存在,直到下电。

想请教一些排查的思路和解决问题的办法,谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好,使用自己设计的PCB在调试中发现,使能PWR_FLOAT现象出错,现象是在DMD上留下一个若隐若现的图像,该图像为使能PWR_FLOAT之前DMD显示的图像,能肉眼看到微镜并没有放平。

在英文论坛与TI工程师交流如下。

目前的主要现象是,①通过下电的方式使能PWR_FLOAT,“残影”存在,但在下电后约2-3s消失;②通过FPGA逻辑使能PWR_FLOAT,“残影”持续存在,直到下电。

想请教一些排查的思路和解决问题的办法,谢谢。

产生这个问题有两个原因,

1. APPS FPGA上电,需要测试:

2. APPS FPGA logic

参考TI代码

https://www.ti.com/lit/zip/dlpc103

或者把你的发过来一起分析。