Part Number: TLIN1028-Q1

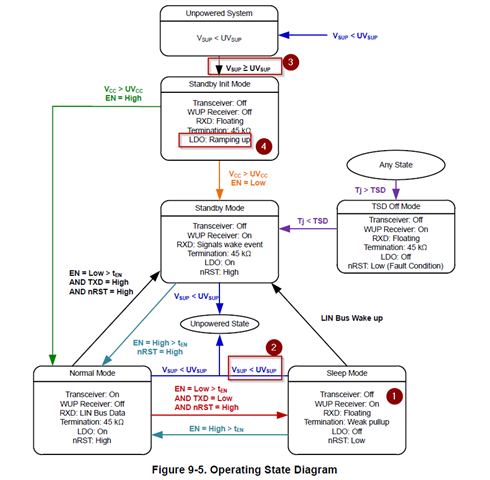

steps for reproduce the failure:

1,configure the system into sleep mode

2,reduce power supply to 0

3,power supply increase again above UVsup

4,the LDO ramping up is not observed as marked in state machine , RST is also keep low.

Question: Could you help explain how this can happen?

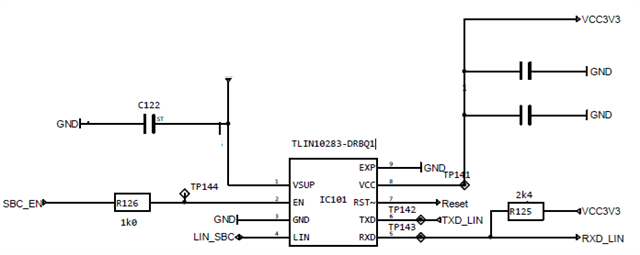

TLIN10283-DRBQ1 used, schematic attached as below