Other Parts Discussed in Thread: DS280DF810

Hi ,

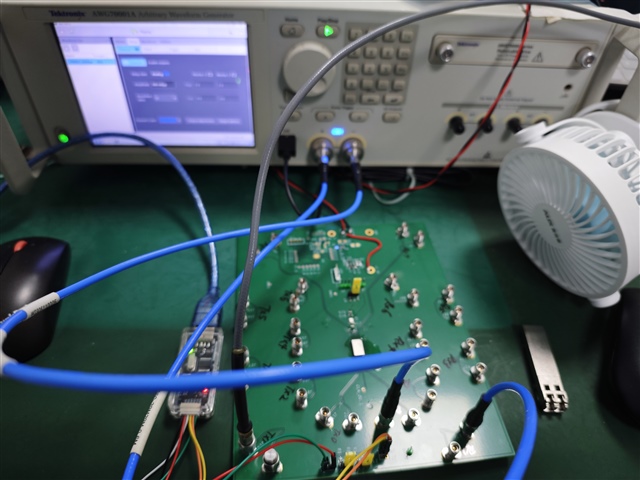

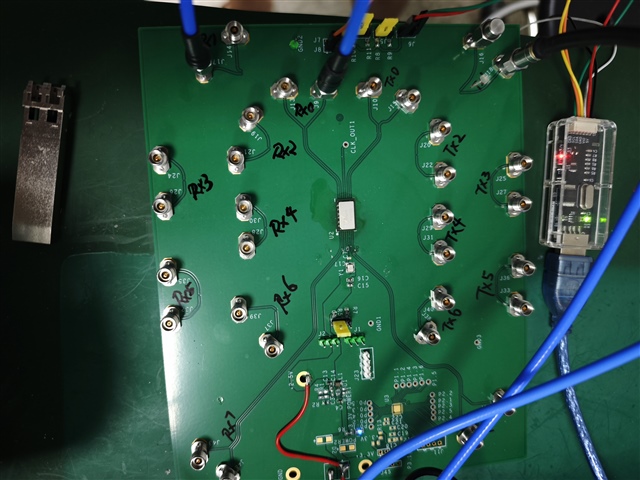

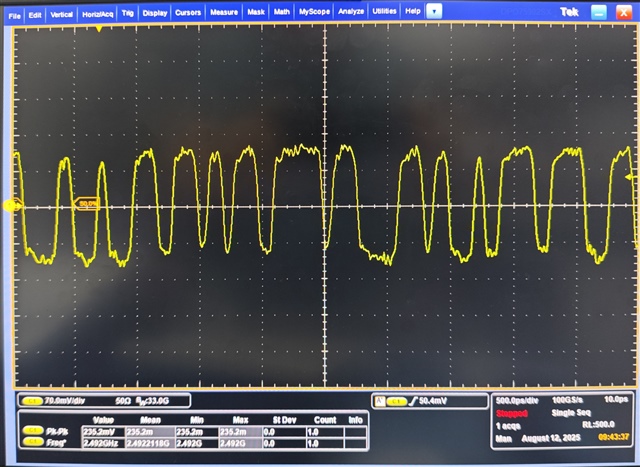

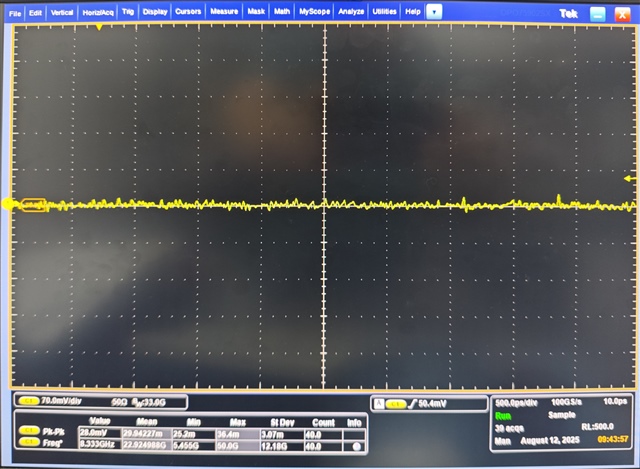

During the debug,I found if no data-rate is applied on the Rx-input channel of the DS280MB810, there is no output when the PRBS generator is enable.would you pls answer: how to turn on the prbs generator funciton when CDR is unlocked(no data-rate on Rx-input channel).

Thanks.