Part Number: DP83822HF

我在使用STM32H735和DP83822进行UDP通信的开发时,遇到以下问题,希望能够帮忙解答,感谢。

1.在此之前我已经成功完成了电口的通信(通过软件寄存器配置RMII MAster模式)。

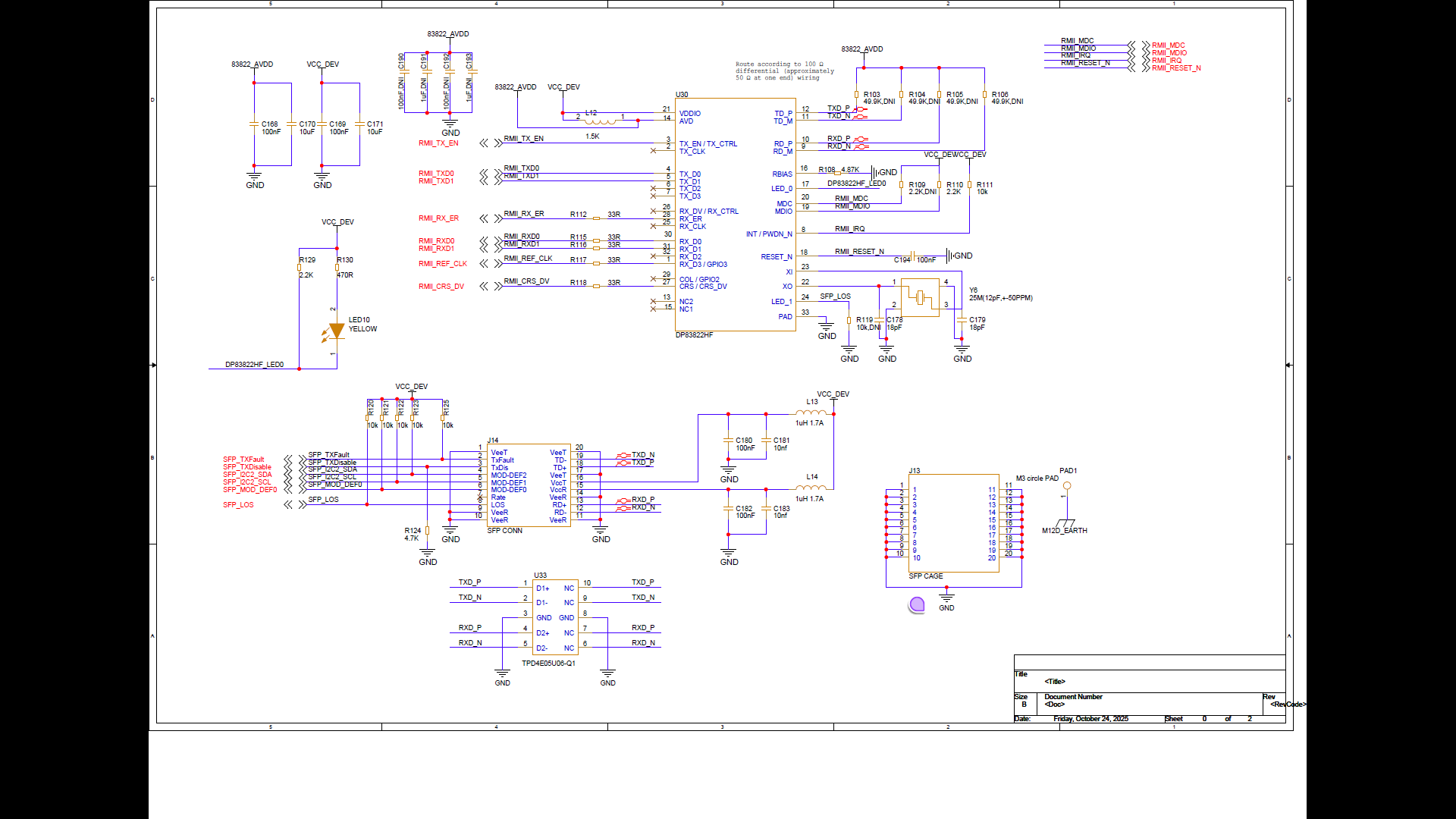

2.现在提供的图片为光口的电路图。基于步骤1的软件配置,我继续进行了如下操作:

(1)使能光纤模式(0x0A:bit14=1);

(2)禁止自动协商,强制100M全双工(0x00:bit12=0,bit13=1,bit8=1)。

但是插上光纤后无任何连接,且灯不亮。

3.请问硬件电路有什么致命错误吗?或者基于此硬件电路设计,软件还需要完成什么其他配置吗?

文末附上我读取的寄存器值,希望能帮忙进行分析,再次感谢。

| DP83822_BMCR | 0x00 | 0x2100 |

| DP83822_BMSR | 0x01 | 0x7849 |

| DP83822_PHYI1R | 0x02 | 0x2000 |

| DP83822_PHYI2R | 0x03 | 0xA240 |

| DP83822_ANAR | 0x04 | 0x01E1 |

| DP83822_ANLPAR | 0x05 | 0x0000 |

| DP83822_ANER | 0x06 | 0x0004 |

| DP83822_ANNPTR | 0x07 | 0x2001 |

| DP83822_ANLNPTR | 0x08 | 0x0000 |

| DP83822_CR1 | 0x09 | 0x0020 |

| DP83822_CR2 | 0x0a | 0x4100 |

| DP83822_CR3 | 0x0b | 0x1000 |

| DP83822_REGCR | 0x0d | 0x401F |

| DP83822_ADDAR | 0x0e | 0x4300 |

| DP83822_FLDS | 0x0f | 0x0000 |

| DP83822_PHYSTS | 0x10 | 0x0004 |

| DP83822_PHYSCR | 0x11 | 0x0108 |

| DP83822_MISR1 | 0x12 | 0x0000 |

| DP83822_MISR2 | 0x13 | 0x0800 |

| DP83822_FCSCR | 0x14 | 0x0000 |

| DP83822_RECR | 0x15 | 0x0000 |

| DP83822_BISCR | 0x16 | 0x0100 |

| DP83822_RCSR | 0x17 | 0x0061 |

| DP83822_LEDCR | 0x18 | 0x0400 |

| DP83822_PHYCR | 0x19 | 0x8021 |

| DP83822_10BTSCR | 0x1a | 0x0000 |

| DP83822_BICSR1 | 0x1b | 0x007D |

| DP83822_BICSR2 | 0x1c | 0x05EE |

| DP83822_CDCR | 0x1e | 0x0002 |

| DP83822_PHYRCR | 0x1f | 0x0000 |