我在使用CDCE62005RGZT这款时钟芯片时遇到了一个问题。

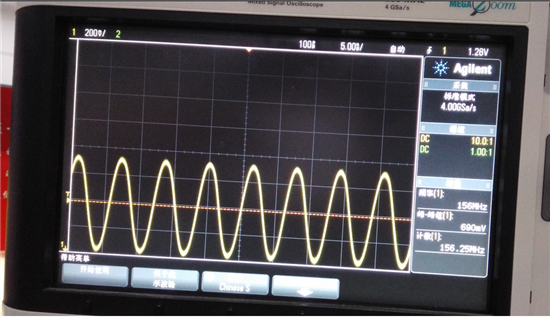

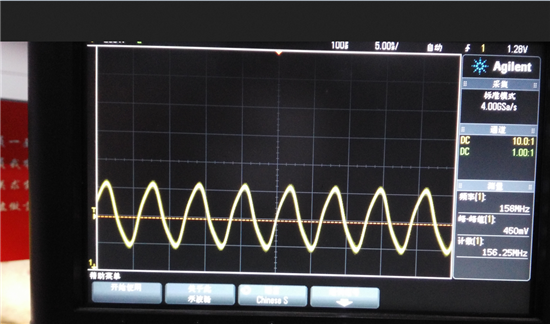

首先我配置CDCE62005RGZT寄存器使U0P、U0N引脚输出156.25MHz的LVDS差分时钟,并成功锁存,用示波器测量U0P、U0N引脚输出的波形是正常的正弦波。 当把U0P、U0N输出的时钟接入到FPGA之后,再用示波器测量U0P、U0N输出的波形,频率依然是156.25MHz,但是波形由正弦波变尖,有点类似三角波,且峰峰值变小(见图),不知道是什么原因导致的,接入负载之后会对CDCE62005RGZT的时钟输出产生影响么?配置的寄存器值见附件。

另外我发现CDCE62005RGZT输出LVDS差分时钟时,输出时钟峰峰值会随输出频率的升高而减小,且输出频率越高,峰峰值减小的更明显,不知道是什么原因。

没加负载之前的波形:

连接FPGA之后的波形:

原理图: