你好:

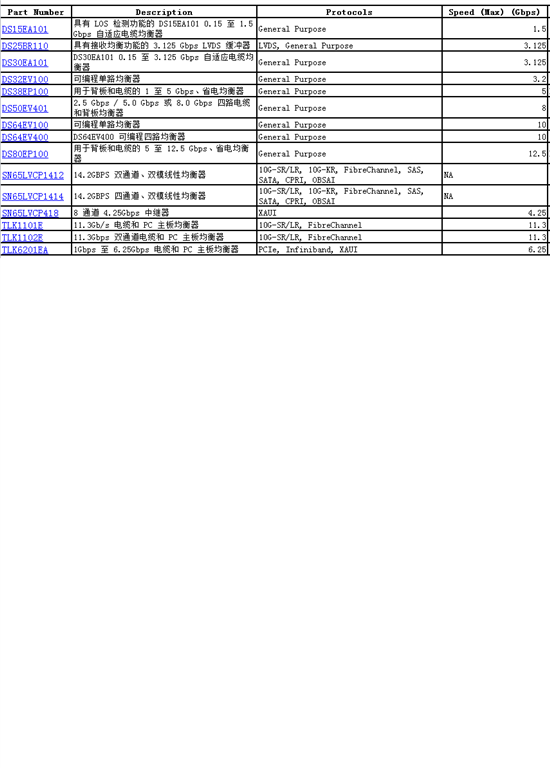

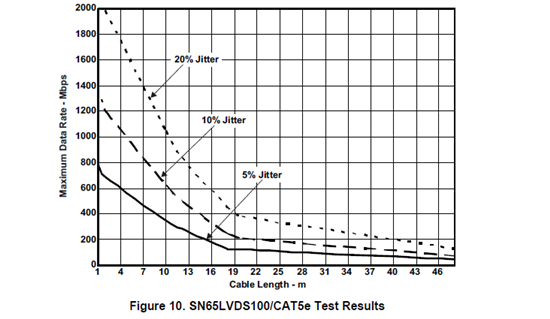

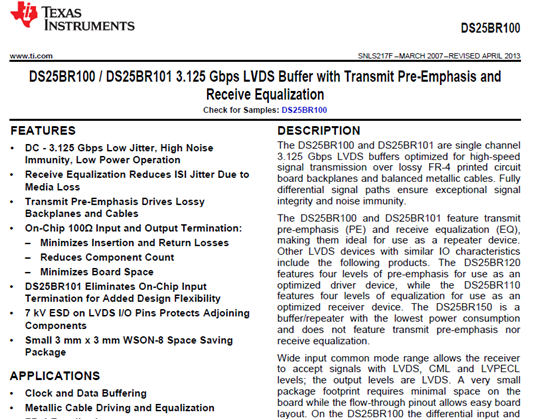

最近涉及一个项目,6U机箱背板中板卡与板卡间的点对点通信,打算走LVDS(通过FPGA的差分IO实现),速率100Mpbs,最长走线大约有600mm,考虑信号完整性等问题,打算选用一个均衡器(带预加重和均衡功能)来实现,但TI官网里面很多均衡器的速率均为几百M至上G,比如DS15EA101,DS25BR110,其中DS15EA101数据手册明确说明支持速率是150Mbps至1.5Gbps,DS25BR110没有明确说支持的最低速率,背板点对点通信速率定在100Mpbs,不知道用上诉两种均衡器有没有问题,如果不行还有没有支持速率更低一些的均衡器。