Other Parts Discussed in Thread: CDCE62002

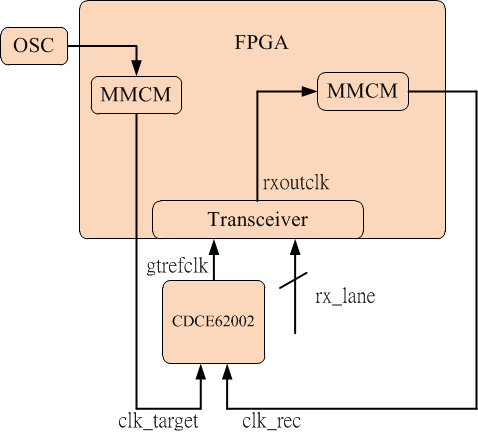

您好, 我正在規劃CDCE62002應用在FPGA線路圖,

主要參考data sheet的9.4.2應用, 具體接法如下圖,

其中, AUX_IN和clk_target連接, REF_IN和clk_rec連接, MMCM是FPGA內的PLL,

(1) AUX_IN是否只能接XTAL, 能否用FPGA LVCMOS33 AC Couple提供時鐘頻率?

(2) Smart MUX如果只選用REF Select和AUX Select, 當從一組切換到另一組的過程中, 會對輸出產生多少瞬間頻偏?

(3) Smart MUX的Auto Select行為為何? initial或unlock時默認使用哪個輸入當參考時鐘?

我的希望initial或unlock時選取AUX_IN, 等到Transceiver和CDCE62002穩定後, 再透過SPI切換到REF_IN,

切換過程中CDCE62002輸出頻偏必須遠小於1000ppm,

謝謝~