在使用DP83848的过程中,经常出现网络芯片无缘无故坏掉的情况,或者有些是找网速度比较慢,网上也查了一些资料,有些说是要在PHY和变压器之间的数据线上面加TVS保护,这个还没有测试,后面会加了测试,另外一个就是说mcu和PHY之间的数据线阻抗不匹配导致的过冲过大也会损坏芯片,不知道是不是这样的,pcb布局的时候是不是TXD和RXD以及TX_CLK、RX_CLK这些线都需要做阻抗匹配到50欧姆,原来的pcb布局是没有做的,在PHY端都加了50欧姆的电阻。

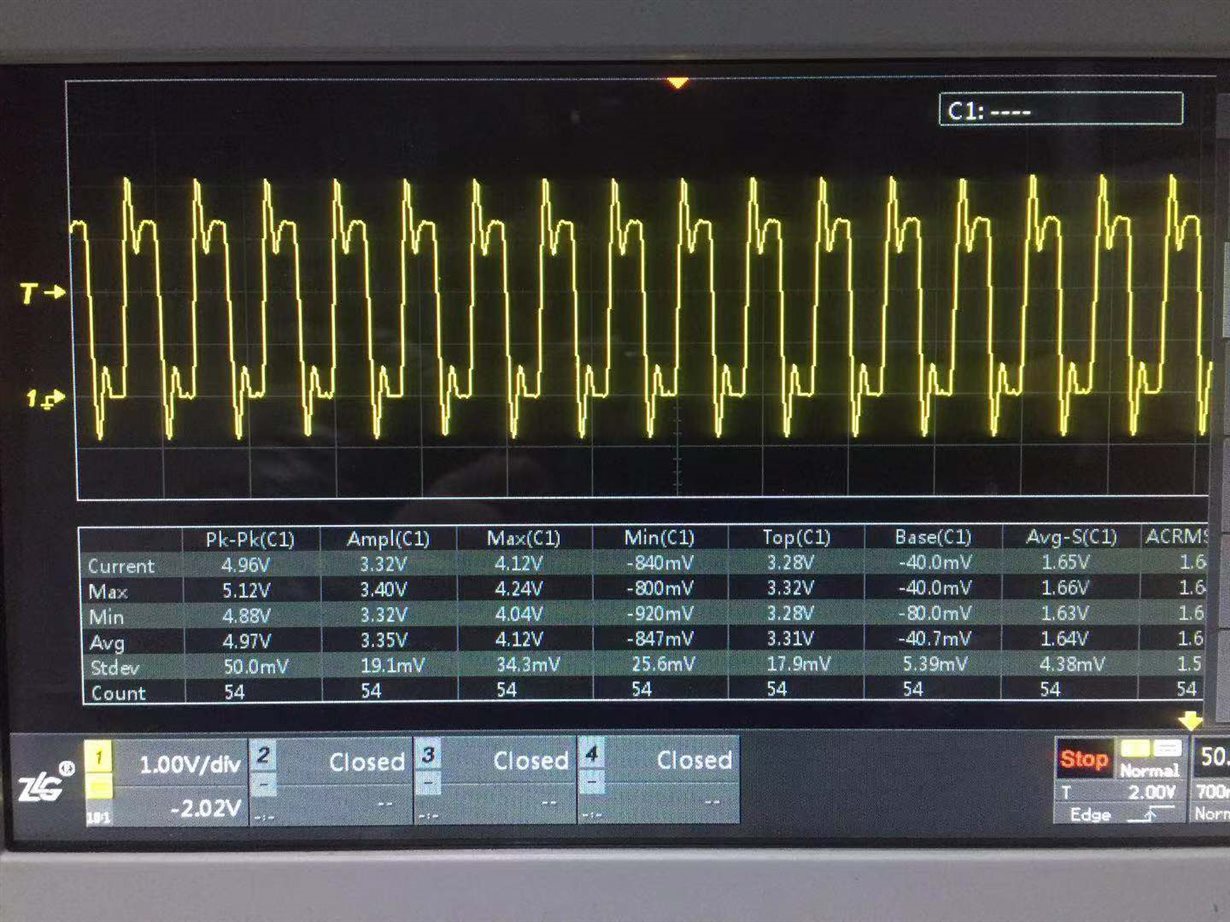

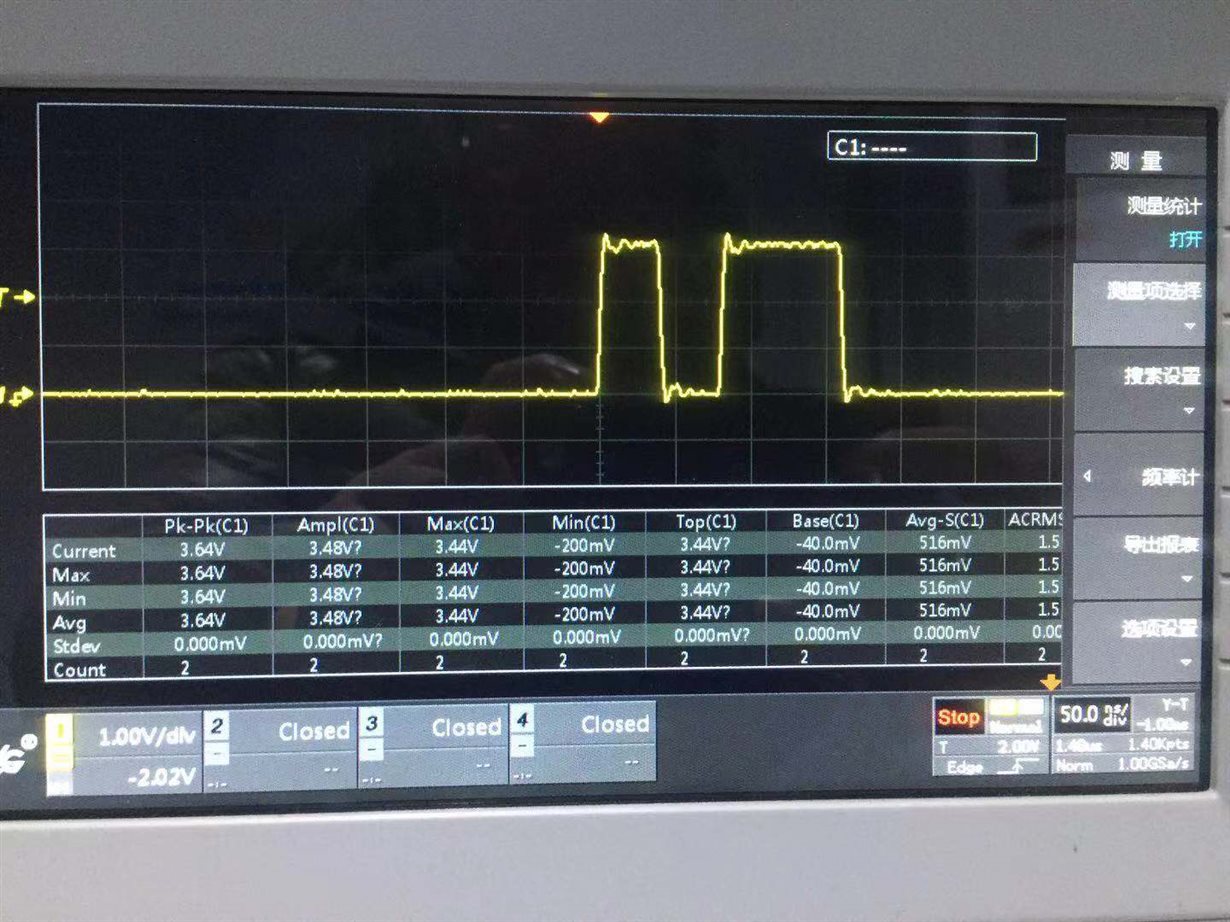

下图是我测试出来TX_CLK、RX_CLK的波形,TXD1上的波形,帮忙看一下,这个时钟的过冲是不是变大,应该如何优化pcb或者调整电路来减小这个过冲,谢谢!