大家好:

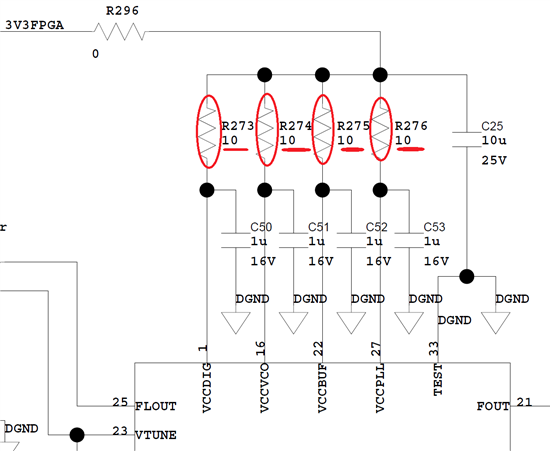

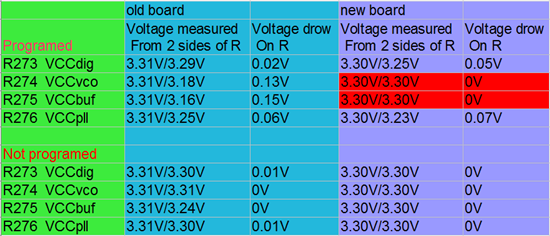

我们有两块相同的PCB板,上面有PLL ‘LMX2531 LQ1500’ 和clock buffer 以及配置他们的FPGA。 第一块板子的PLL工作正常(输入10M,输出1.5G)。但第二块板子上的PLL没有输出。两块PCB板布线和器件都是一样的,只是PCB厂家不一样而已。 而且第二块板子中我们测试了他的时钟输入, LE,CE在配置后都是到所需的状态。 用的FPGA配置程序也是一样的。 后来我们认为是pll芯片出问题,就换了一个新的PLL新片,但仍然没有输出。而且我们将输出端(到clock buffer)切断,再通过一个49欧左右的电阻接地。 仍然是没有输出。

各位有什么新的想法?实在是想不出什么来解决定位这个问题。

谢谢~~