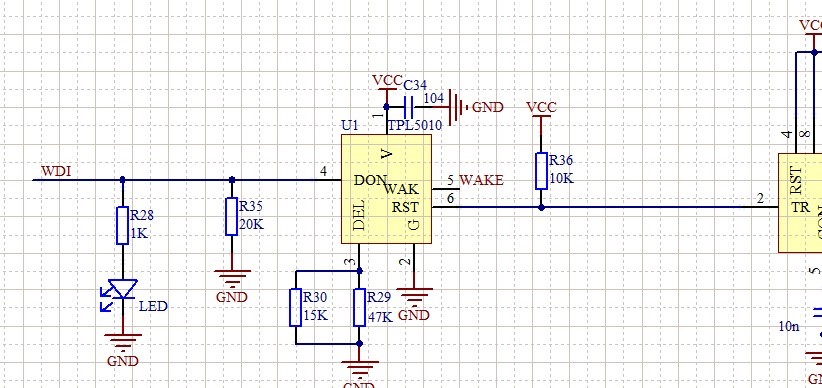

我使用的电路如下图,但在实际使用时发现,上电后,RST脚在电源上电后400MS后才会拉高,这样就把我的后面电路误触发了。想问下是否有其他办法让电源上电后,RST脚立即被拉高?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

10s的话没问题,能使得RST为低电平的两个原因:

RSTn is asserted (LOW) for either one of the following conditions:

1. If the DELAY/M_RST pin is high for at least two consecutive cycles of the internal oscillator (approximately 20 ms).

2. At the beginning of a new time interval if DONE is not received at least 20 ms before the next WAKE rising edge (see Figure 8)

所以,电路中我看到 DELAY/M_RST 这个引脚一直拉低的对吧?排除它对RST的影响。

其次就是第二点,电路中, done信号悬空接的吗?最好也检查下焊接情况。

最后,就是您这里提到上电就拉高,事实上,RST拉高也是需要等VDD上电起来稳定之后,至少需要ttR_EXT + tRSTn的时间,请参考Figure