Dear TI Engineer,

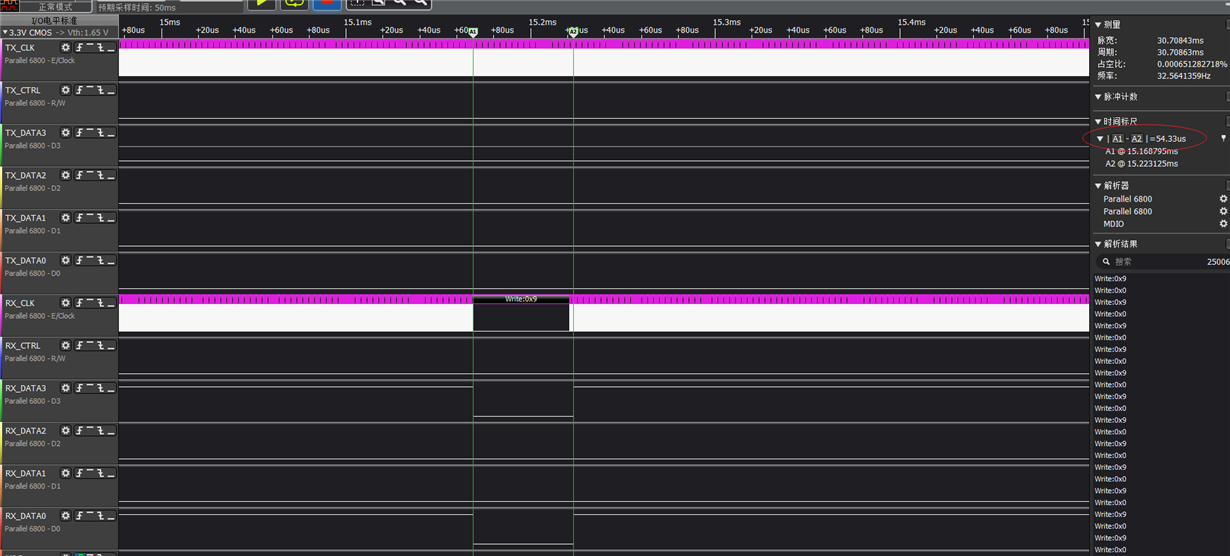

我们在使用DP83867E时出现RX_CTRL输出异常的情况,配置如下:

1. DP83867E作为RGMII接口使用

2. 使用DP83867E内部LOOP功能

3. DP83867E与我们的MAC TX连接,LOOP输出连接我们的MAC RX

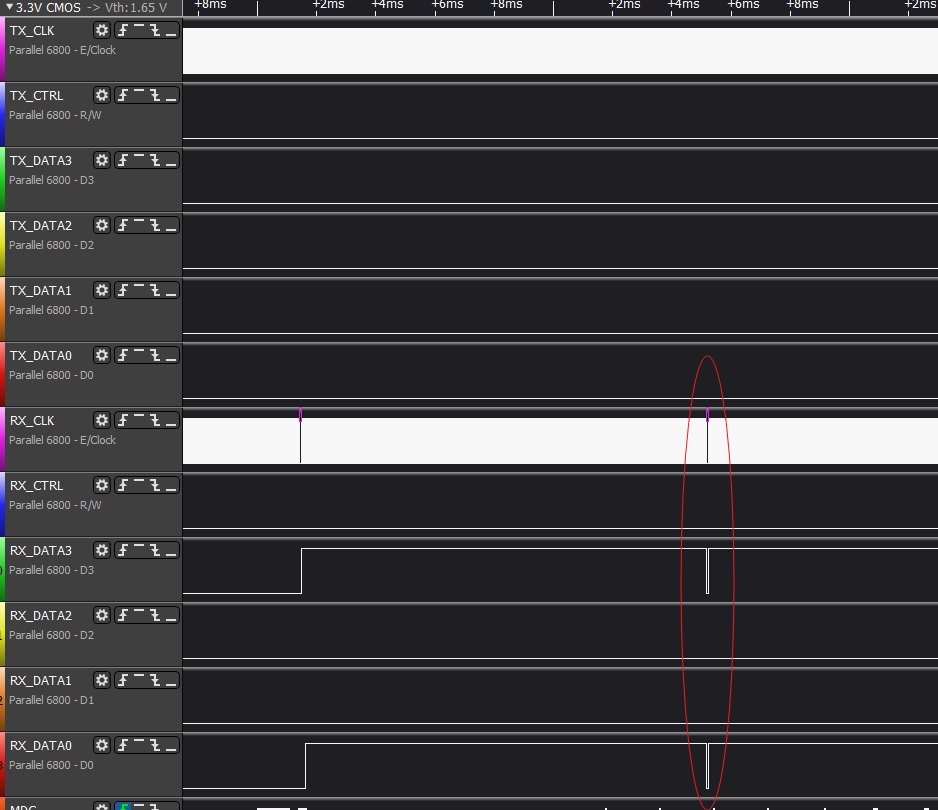

4. MAC输出RGMII 100M数据,示波器观测TX CTRL在数据传输中一直为High Level

5. 示波器观测经过DP83867E输出的RX CTRL信号有不规则的低脉冲产生

6. 最终导致MAC收到的数据异常,主要为接受的数据有不规则的丢失数据

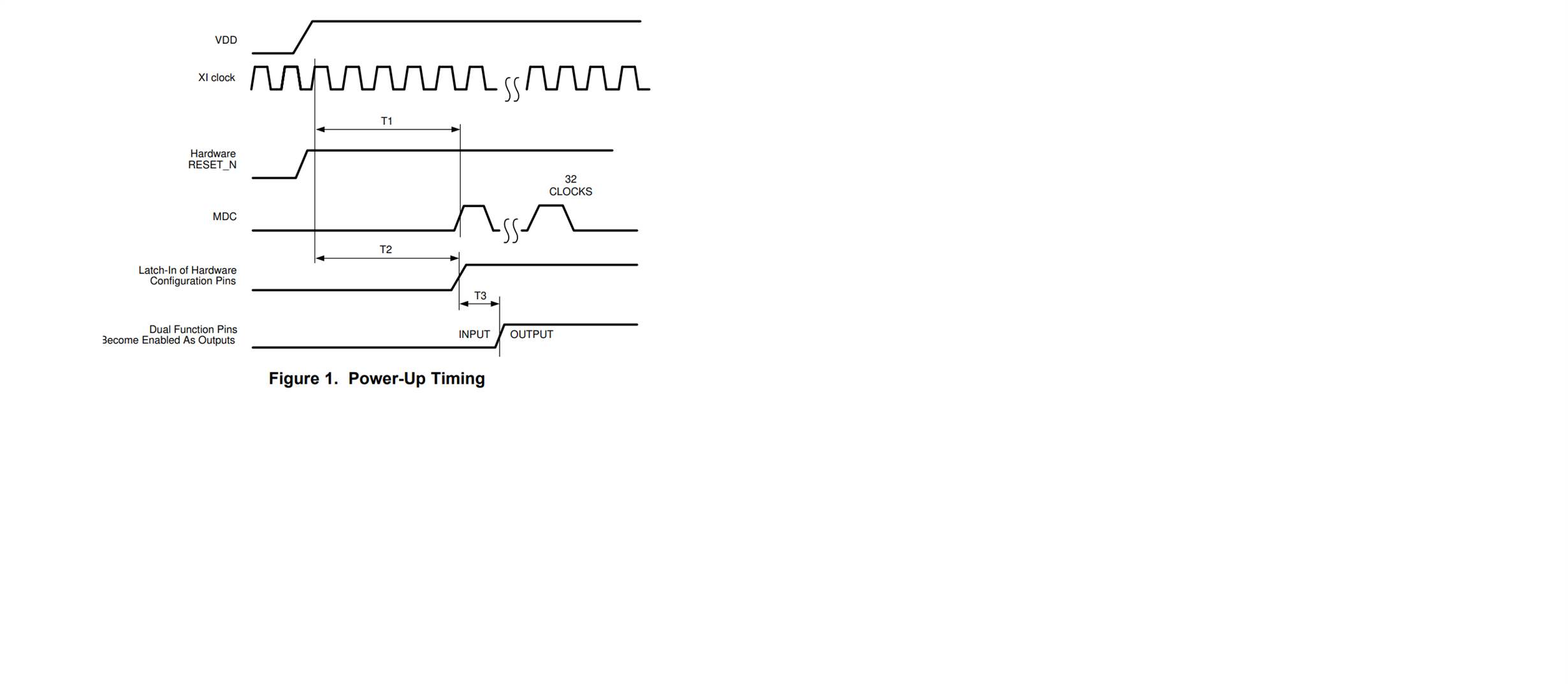

想咨询下,该情况是否为MAC输入的数据存在Setup/hold Violation导致的?能否提供处理方案?