Part Number: DP83848YB

Other Parts Discussed in Thread: SN65CML100

如图所示,两个49.9Ω之间为什么需要接3.3V

如图所示,两个49.9Ω之间为什么需要接3.3V

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DP83848YB

Other Parts Discussed in Thread: SN65CML100

如图所示,两个49.9Ω之间为什么需要接3.3V

如图所示,两个49.9Ω之间为什么需要接3.3V

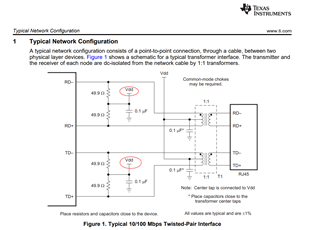

您好,49.9ohm接VDD的目的是建立合适的偏置电压。3.3V的VDD的话,Vbias=1.65V。

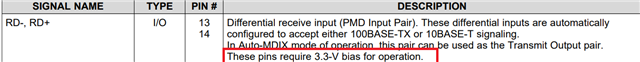

抱歉说错了,不是偏置到1.65V,是偏置到3.3V,RX+-需要偏置到3.3V,这个在datasheet中有描述:

另外,您这里提到了这款PHY是电流型的PHY,所以附上一篇关于功耗计算的应用手册:

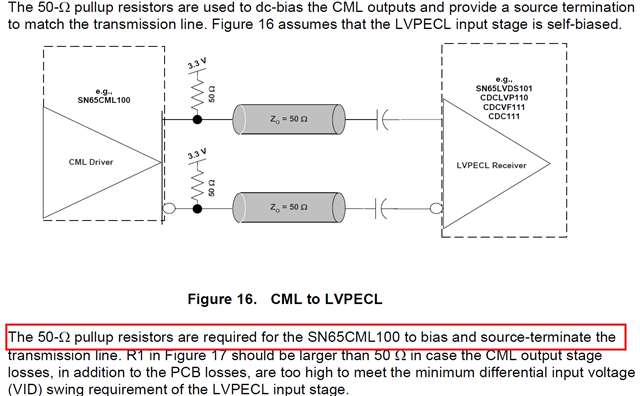

您好,抱歉回复晚了, DP83848的TD和RD是CML电平,CML和其他电平耦合时,需要上拉49.9ohm/50ohm到VCC。典型器件可以参考SN65CML100的数据手册有描述。另外,我这里也有CML和LVPECL AC耦合的典型应用:

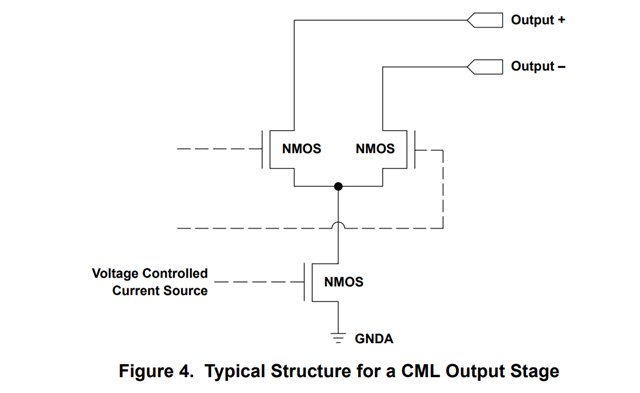

不是的,看下CML driver的输出架构,它是由一个电压控制的电流源以及两个NMOS的集电极组成的差分对,或者说是开漏输出,开漏输出需要上拉才能输出逻辑高,否则只能逻辑低。截图的应用手册可以参考:https://www.ti.com/lit/an/slla120/slla120.pdf