Hi Ti工程师,

我们在应用TCA9803做buffer时,尽管链路功能没问题,IIC数据可以通,但是测试波形不是很理想,想咨询下解决方案优化。具体情况如下:

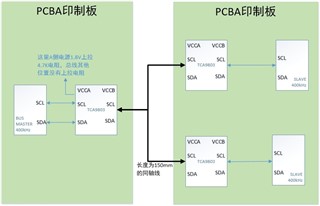

我们应用的IIC buffer拓扑结构和电路板实物如下:

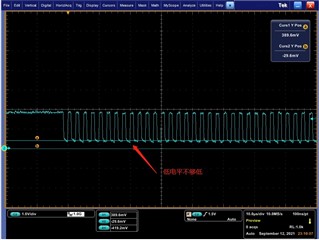

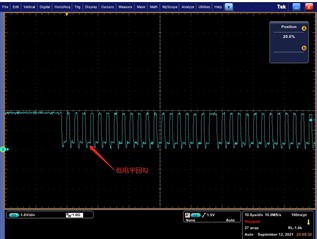

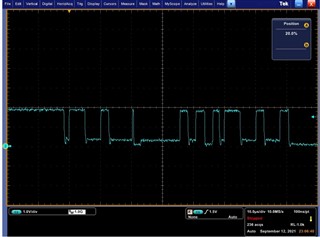

我们在slave端测试到的IIC波形如下,有一路II0的SCL信号低电平有个回勾式的台阶,且SDA信号极差;另一路IIC1是SCL的低电平有,不够低,且SDA的信号质量也差。这两路IIC Master不是同一路,异常现象不一致。

1、IIC0总线 slave上的波形

2、IIC1总线的slave时钟