Part Number: DS100RT410

Other Parts Discussed in Thread: CDCL1810A

1,问题背景:

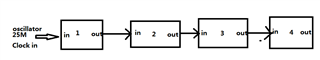

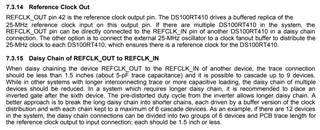

4个DS100RT410级联使用时,每2片retimer输出4x10G seders,第一片DS100RT410 引脚 REFCLK_IN接到25M oscillator ,并通过REFCLK_OUT引脚接到第二片的DS100RT410的REFCLK_IN引脚,第三、四片的DS100RT410也是如此。

2,问题描述:

目前测试发现的问题是:

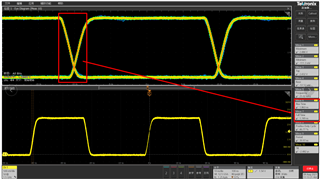

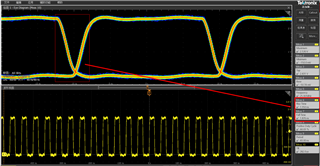

因走线插损的原因,第2、3、4片的DS100RT410 引脚 REFCLK_IN时钟信号rise time和fall time的f逐片变大,如下图。

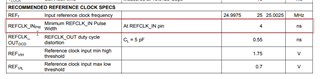

第二片DS100RT410 引脚 REFCLK_IN时钟信号:rise time=1.862ns,fall time=1.749ns

第三片DS100RT410 引脚 REFCLK_IN时钟信号:rise time=1.950ns,fall time=1.876ns

3,问题决策:

请帮忙确认评估问题描述中的时钟信号质量是否这个对DS100RT410 的工作有影响,主要风险是什么?