Part Number: DS90UB941AS-Q1

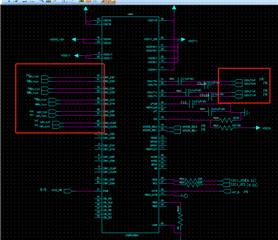

硬件设计上是只接了DSI0 能支持到1080p60的dual link mode的输出吗? 有寄存器参考配置吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,1080p60 需要像素时钟频率为148.5MHz,而941AS的dual link的像素时钟为210Mhz。所以是可以支持的。

并且datasheet中也有描述:

Supports pixel clock frequency up to 210 MHz for 3K (2880x1620) at 30Hz, QXGA (2048x1536), 2K (2880x1080), WUXGA (1920x1200), or 1080p60 (1920x1080) resolutions with 24-bit color depth。

dual link模式下,如果和948或940搭配使用的话 ,是自动可以识别的,不需要单独配置dual link 模式。

或者也可以通过寄存器DUAL_CTL1 配置为force dual link mode。

不好意思,需要补充下,刚看到您的电路是只接了DSI0, 那么这种情况下只能是single link mode的呢。

无法配置为dual link mode。

您好,不好意思,是的,上图这种使用两个deserilaizer的也是dual link。 single link和dual link的定义是通过下行端口即receiver 或者传输的视频源来决定的,

比如derseralizer 使用948或者940,输入有两个通道,所以941 和948或者941连接的时候就是dual link。

比如928或者926输入只有一个通道,那么就是single link。

所以按照您的描述,输出TX0 和TX分别和deserailzier的RX0和RX1连接的话, 即为dual link。

但是dual link的话,每个通道像素时钟为一半,即最高105Mhz,而1080p60的话需要148.5MHz的像素时钟,所以是不能同时输出两路1080p60分辨率的。

您可能理解错我的意思了

我的意思是 两个link 组成一个1080p60. 而不是 每个link都是1080p60

确认下您的应用,单通道DSI0 输入,输出双路DOUT0 和DOUT1,分别接两个deserializer是吗?

如何将两个link组合成一个1080p60,DSI0和DSI1 两路输入,然后输出一路1080P60?

单通道DSI0 输入,输出双路DOUT0 和DOUT1 ,接一个deserializer,一个948 deserializer 配合使用不行吗?

可以,也就是说941 DSI0 输入,DOUT0和DOUT1 输出,接948。 相当于948 dual link 输入,948的输出可以是single OpenLDI输出也可以是dual OLDI输出,但是时钟都能达到192Mhz,所以1080p60是支持的。

您好,我的理解是,如果948 这边OLDI 需要1080p60 输出,那么FPD link端也需要支持1080p60.

而对于DS90UB941来说,如果只使用DSI0 single input,像素时钟最大为105Mhz, 这样的话941的FPD link端是无法支持1080p60输出的,所以需要941也是dual DSI input才行。

所以如果只是用DSI0或者DSI1 input, 整个架构应用是没问题的,但是对于948这端来说输出是达不到1080p60的,720p没问题,因为941的single input时钟为105Mhz。

先不考虑我们用的什么derseralizer

只是用DSI0 input, dual link 输出的话, 整个架构应用是没问题的 那这个我941应该怎么配置呢、?

寄存器0x4F DUAL_DSI_EN bit6=0 single DSI mode。

DSI_PORT_SEL bit50 DSI port 0

bit[3:2]=11 4lane

dual link 输出,寄存器0x5B bit[2:0].可以配置为force dual link mode,即011, 也可以配置为: Auto-Detect FPD link mode 即为000.

另外就是寄存器0x01,可以enable DSI input。

enable DSI input以及DSI lane selection 既可以通过寄存器配置,也可以通过MODE_SEL[1:0] pin 配置,参考Table8-8.

输出port0 和port1的 那个clk 不知道怎么配,寄存器0x42 选择port0 要配一次 选择port1 要配一次?

我目前配置如下:

{0x01,0x08}, //Disable DSI

{0x1E,0x01},

{0x1E,0x04},

{0x1E,0x01},

{0x03,0x9A},

{0x1E,0x01},

{0x40,0x04},

{0x41,0x21},

{0x42,0x60},

{0x1E,0x02},

{0x40,0x04},

{0x41,0x21},

{0x42,0x60},

{0x1E,0x01},

{0x5B,0x03},

{0x4F,0x8C},

{0x1E,0x01},

{0x40,0x04},

{0x41,0x05},

{0x42,0x18},

{0x1E,0x02},

{0x4F,0x8C},

{0x1E,0x02},

{0x40,0x04},

{0x41,0x05},

{0x42,0x18},

{0x01,0x00}, //Enable DSI

输出port 0 和输出port1 配置好之后,不需要配置DSIx_CLKP/N, 因为每个link 都包含一对clock+4 对data。所以配置FPD link port0或者port1 是把clock包含在内的。

间接寄存器0x40~0x42 是在初始化的时候enable DSI input之前需要加上的。datasheet 中的配置例子因为是配置的impedant 2:2 mode,单独对port 0 和port1 分别进行了配置,所以配了两次。

在您的应用中,FDP link 配置为dual link,我认为在enable DSI input之前配置一次就好了。

配置DSIx_CLKP/N 这个不是得选 port ,不选port 直接配置也行?

而且941内部需要 split 分奇偶信号嘛 不然那这个数据图像怎发送的 ?

两个link 都发送1080p?

这个问题我需要再确认下。

另外,如果您是Single DSI -> 941AS -> Dual FPD -> 948 -> Display这个应用,是可以支持到1080p的。

Single DSI -> 941AS -> Dual FPD -> 948 -> Display这个应用,是可以支持到1080p的

能提供下参考配置吗?

您好,下面是941AS配置为1080p的例子,请参考:

# 1920x1080p60, Dual Link FPD III

# PCLK = 148.5MHz

# DSI clock = 445.5MHz

# DSI Lane Speed = 891Mbps/lane

# 4 Lanes DSI

# DSI input port 0

# DSI non-burst mode with sync pulses

# MODE_SEL0 strap = No. 3

# MODE_SEL1 strap = No. 0 or 1

import time

UB941AS = 0x18

board.WriteI2C(UB941AS,0x01,0x02) # Reset

time.sleep(0.1)

board.WriteI2C(UB941AS,0x01,0x08) # Disable DSI

board.WriteI2C(UB941AS,0x40,0x04) # TSKIP_CNT

board.WriteI2C(UB941AS,0x41,0x05) # TSKIP_CNT

board.WriteI2C(UB941AS,0x42,0x30) # TSKIP_CNT

board.WriteI2C(UB941AS,0x40,0x10) # Init DSI Clock Settings (From Section 10.2 of datasheet)

board.WriteI2C(UB941AS,0x41,0x86) # Init DSI Clock Settings (From Section 10.2 of datasheet)

board.WriteI2C(UB941AS,0x42,0x0A) # Init DSI Clock Settings (From Section 10.2 of datasheet)

board.WriteI2C(UB941AS,0x41,0x94) # Init DSI Clock Settings (From Section 10.2 of datasheet)

board.WriteI2C(UB941AS,0x42,0x0A) # Init DSI Clock Settings (From Section 10.2 of datasheet)

board.WriteI2C(UB941AS,0x01,0x00) #Release DSI

board.WriteI2C(UB941AS,0x40,0x10) # Init DSI Clock Settings (From Section 10.2 of datasheet)

board.WriteI2C(UB941AS,0x41,0x86) # Init DSI Clock Settings (From Section 10.2 of datasheet)

board.WriteI2C(UB941AS,0x42,0x0A) # Init DSI Clock Settings (From Section 10.2 of datasheet)

board.WriteI2C(UB941AS,0x41,0x94) # Init DSI Clock Settings (From Section 10.2 of datasheet)

board.WriteI2C(UB941AS,0x42,0x0A) # Init DSI Clock Settings (From Section 10.2 of datasheet)

您好 ,这个还是没看懂

看datasheet 里面0x86 0x94 这两个寄存器 没明白 能说明下吗?

而且0x94是针对DSI1 的配置 应该不需要吧

如上参考配置:只对 TSKIP_CNT这个配置了, DSI input , Lane ,FPD Link mode 全都没有呀 ,你确定可以?

这只是一个基本的使用941AS应用1080p的配置,并不是完整例程,所以您说的 DSI input , Lane ,FPD Link mode 都是需要再配置的。

另外,您也可以将您的问题提交到英文E2E论坛上,由美国的资深工程师给您解答。https://e2e.ti.com/support/interface-group/

如果主机和941接在一起, 那么需要配置的是941,948和display在整个link中都作为slave。

您好,我们有专门FPD link的培训视频,您可以参考一下,

https://training.ti.com/fpd-link-learning-center?context=1134310

另外我这边发现您也咨询了同样的问题在另一个帖子里,您可以参考上面关于FPD link的培训视频,也可以参考同事的建议,登录英文E2E咨询美国工程师。