Other Parts Discussed in Thread: ALP, USB2ANY

Hi Ti supporter,

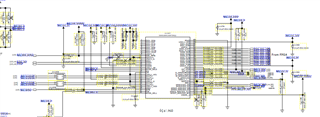

硬件连路:fpga dsi0 -> 941 dsi0 -> DOUT0 、DOUT1 -> 2路948 panle,

fpga dsi1 -> 941 dsi0 -> DOUT0 、DOUT1 -> 2路948 panle,

下图是一路941电路图。

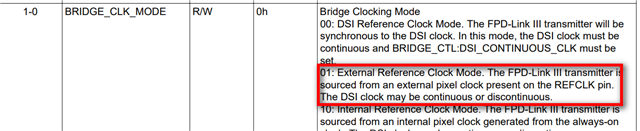

目前还在调试941-〉948通路阶段,设置941 patgen 输出color bar video数据到948,

941 patgen采用内部clk,发现948 无法lock pll clock (0x3c[0] 为0),测量948 LOCK pin电平为0.7v

屏没有显示。

附件是941 、948 reg dump 和 init code,请帮忙检查下哪里设置有问题。

//config vido

//941 dsi input config(Single-DSI mode,Select DSI Input port 0,4 Lanes)

TiSerdes_I2C_Write_Mask(ti941_addr, 0x4F, 0x0C, 0x6C);

//941 Dual FPD-Link III mode (Single, Dual, or Replicate)

TiSerdes_I2C_Write_Mask(ti941_addr, 0x5B, 0x3, 0x07);

TiSerdes_I2C_Write(ti941_addr, 0x17, 0x9e);

//config video

//948 Dual link based on received data

TiSerdes_I2C_Write_Mask(ti948_addr, 0x34, 0x8, 0x18);

//948 Dual FPD/OLDI output

TiSerdes_I2C_Write_Mask(ti948_addr, 0x49, 0, 0x03);

//config backlight

//enable 948 bl pin

TiSerdes_I2C_Write(ti948_addr, 0x1f, 0x09);

//pg

dm_i2c_reg_write(ti941_addr, 0x66, 0x03);

dm_i2c_reg_write(ti941_addr, 0x67, 0x02);

dm_i2c_reg_write(ti941_addr, 0x66, 0x04);

dm_i2c_reg_write(ti941_addr, 0x67, 0xf8);

dm_i2c_reg_write(ti941_addr, 0x66, 0x05);

dm_i2c_reg_write(ti941_addr, 0x67, 0xe7);

dm_i2c_reg_write(ti941_addr, 0x66, 0x06);

dm_i2c_reg_write(ti941_addr, 0x67, 0x33);

dm_i2c_reg_write(ti941_addr, 0x66, 0x07);

dm_i2c_reg_write(ti941_addr, 0x67, 0x80);

dm_i2c_reg_write(ti941_addr, 0x66, 0x08);

dm_i2c_reg_write(ti941_addr, 0x67, 0x07);

dm_i2c_reg_write(ti941_addr, 0x66, 0x09);

dm_i2c_reg_write(ti941_addr, 0x67, 0x2d);

dm_i2c_reg_write(ti941_addr, 0x66, 0x0A);

dm_i2c_reg_write(ti941_addr, 0x67, 0x28);

dm_i2c_reg_write(ti941_addr, 0x66, 0x0B);

dm_i2c_reg_write(ti941_addr, 0x67, 0x0a);

dm_i2c_reg_write(ti941_addr, 0x66, 0x0C);

dm_i2c_reg_write(ti941_addr, 0x67, 0x28);

dm_i2c_reg_write(ti941_addr, 0x66, 0x0D);

dm_i2c_reg_write(ti941_addr, 0x67, 0x32);

dm_i2c_reg_write(ti941_addr, 0x65, 0x04);//0x0c selsct dsi clk

dm_i2c_reg_write(ti941_addr, 0x64, 0x35);

dm_i2c_reg_write(ti941_addr, 0x17, 0x9e);

//941

18 00 00 9a 00 00 58 00 00 01 4c 02 03 30 00 00

00 00 00 8f 00 00 fe 9e 7f 7f 01 00 00 00 01 00

0b 00 25 00 00 00 00 00 01 20 20 a0 00 00 a5 5a

00 09 00 05 0c 00 00 00 00 00 00 00 00 00 81 02

10 90 00 00 00 00 00 00 00 00 00 00 00 00 00 8c

16 00 00 00 02 10 00 02 00 00 12 03 07 06 44 00

22 02 00 00 35 04 0d 32 00 00 00 00 00 00 20 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 7e 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 82 00 78 00 00 44 40 00 00 00 00 02 ff 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 82 00 68 08 00 00 00 00 00 00 00 02 00 00

5f 55 42 39 34 31 00 00 00 00 00 00 00 00 00 00

//948

58 04 00 f0 fe 9e 00 18 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 01 00 00 32 13 53 09

05 00 40 30 08 00 83 84 21 00 00 00 00 00 00 00

00 00 90 25 09 00 00 ac 00 00 00 17 20 e0 23 00

43 03 03 00 60 88 00 00 0f 80 00 08 00 00 63 00

03 10 00 01 80 00 00 00 00 7f 20 20 00 00 00 00

00 00 00 00 10 00 00 00 00 00 00 00 00 00 01 00

00 00 00 07 07 08 00 00 00 00 00 00 02 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 8c 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 c0 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

5f 55 42 39 34 38 00 00 00 00 00 00 00 00 00 00