Other Parts Discussed in Thread: SN65DSI85, SN65DSI83

问:SN65DSI83、SN65DSI84 和 SN65DSI85 上的线时间是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

答:显示面板时序由两个主要参数组成:帧和线。

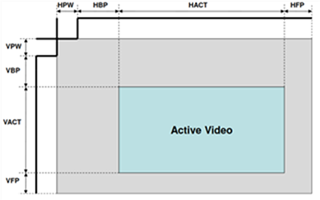

一个帧包含整个显示区域,由多条水平线组成。在每条线的末尾,一个 HSYNC 脉冲(包括一个前沿 HFP、一个后沿 HBP 和宽度 HPW)表示一条新线的开始。这将持续到帧结束,其中 VSYNC 脉冲(也包括一个前沿 VFP、一个后沿 VBP 和宽度 VPW)表示新帧的开始。

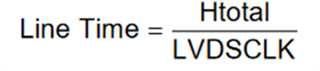

“线时间”是完成线传输所需的时间。换句话说,它表示两个连续 HSYNC 脉冲(或一个 VSYNC 脉冲到下一个紧接着的 HSYNC 脉冲)之间的时间量。在 SN65DSI83、SN65DSI84 和 SN65DSI85 的输出中,可通过以下公式计算线时间(以微秒为单位):

其中 Htotal 是水平像素的总数,LVDSCLK 是 LVDS 时钟的频率(以 MHz 为单位)。例如,如果 Htotal = 1054 且 LVDSCLK = 70.6MHz,则线时间为 14.92us。

在 DSI 端,线时间的定义相同:

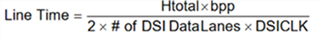

它是两个连续 HSYNC 脉冲(或一个 VSYNC 脉冲到下一个紧接着的 HSYNC 脉冲)之间的时间量。

但 DSI 端的线时间(以微秒为单位)公式不同:

其中 Htotal 是水平像素的总数,bpp 是每像素的位数(18bpp 或 24bpp),DSICLK 是 DSI 时钟的频率(以 MHz 为单位)。例如,如果 DSI 侧的 Htotal = 2108,bpp = 24,DSICLK = 423.6MHz,并且有 4 个 DSI 数据通道,那么 DSI 侧的线时间为 14.92us。

为了让这些器件正常运行,DSI 侧的线时间必须与 LVDS 侧的线时间完全匹配。这是因为这些器件不会重新对齐任何时序。为了使 DSI 至 LVDS 转换正常工作,必须对齐时序。

有关正确配置这些器件的更多信息,以及针对潜在问题的调试步骤,请参阅以下常见问题解答: