Part Number: DS90UB949-Q1

Hi

DS90UB949-Q1导入EDID后,切换到HDMI后无法显示。

EDID按照1920*1080的Display参数设定,HDMI线接到电脑,电脑只能识别出1280*720.

导入其他开发过项目的EDID(1920*720), 电脑端能够识别出1920*720.

不清楚什么原因导致EDID修正也不能让电脑端识别出正确的分辨率。

以上

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS90UB949-Q1

Hi

DS90UB949-Q1导入EDID后,切换到HDMI后无法显示。

EDID按照1920*1080的Display参数设定,HDMI线接到电脑,电脑只能识别出1280*720.

导入其他开发过项目的EDID(1920*720), 电脑端能够识别出1920*720.

不清楚什么原因导致EDID修正也不能让电脑端识别出正确的分辨率。

以上

您好,我不知是不是EDID的配置,以及导入的流程是否都正确。 我的建议是您参考下这个帖子关于“如何实现新的HDMI输入的分辨率”,里面包含了如何对EDID进行读写过程,以及如果Display不支持导入的EDID,提供了EDID编辑器,您参考下:

Hi Kallyn,

导入EDID后HDMI不能显示是问题已经解决,新出现一个问题,样机开机后默认显示内部画面(由Pattern Generator生成画面输出),接下去切换为HDMI显示,可以正常显示HDMI画面,再要从HDMI画面切换成内部画面就无法再切换成内部画面。

1) 内部画面切换到HDMI画面: 949相关寄存器设定:

Add Value

0x64: 0x05 ---> 0x10

0x65: 0x04 ---> 0x00

2) HDMI画面切换到内部画面: 949相关寄存器设定:

Add Value

0x64: 0x10 ---> 0x05

0x65: 0x00 ---> 0x04

此时画面无法显示,需要将0x65: 0x00 ---> 0x0C才可显示出内部画面

再次显示内部画面时时钟源无法切换为内部时钟源,一定要参考外部时钟源,协助确认下会是什么原因导致?

以上

您好,外部时钟是多大频率的?是不是显示屏的分辨率正好和外部时钟源的频率一致,而内部晶振的时钟和显示屏分辨率不匹配,所以导致只能使用外部时钟才能显示画面。

Hi Kally

外部时钟的频率为133.71MHz, 内部测试画面的频率为141.18MHz。

上电默认显示内部测试画面是OK的

具体操作:上电->显示内部测试画面 OK --> 切换到HDMI画面 OK --> 切换到内部测试画面 NG

下面是内部测试画面相关设定:

/*Set divider*/

{E_LVDS949_ADDRESS, 0x66, 0x03 },

{E_LVDS949_ADDRESS, 0x67, 0x11 },

/* Active H/V width */

{E_LVDS949_ADDRESS, 0x66, 0x07 },

{E_LVDS949_ADDRESS, 0x67, 0x80 },

{E_LVDS949_ADDRESS, 0x66, 0x08 },

{E_LVDS949_ADDRESS, 0x67, 0x87 },

{E_LVDS949_ADDRESS, 0x66, 0x09 },

{E_LVDS949_ADDRESS, 0x67, 0x43 },

/* Set Frame size */

{E_LVDS949_ADDRESS, 0x66, 0x04 },

{E_LVDS949_ADDRESS, 0x67, 0xEC },

{E_LVDS949_ADDRESS, 0x66, 0x05 },

{E_LVDS949_ADDRESS, 0x67, 0xB7 },

{E_LVDS949_ADDRESS, 0x66, 0x06 },

{E_LVDS949_ADDRESS, 0x67, 0x45 },

/*Set Back Porch*/

{E_LVDS949_ADDRESS, 0x66, 0x0c },

{E_LVDS949_ADDRESS, 0x67, 0x20 },

{E_LVDS949_ADDRESS, 0x66, 0x0d },

{E_LVDS949_ADDRESS, 0x67, 0x19 },

/*Set Sync Width*/

{E_LVDS949_ADDRESS, 0x66, 0x0a },

{E_LVDS949_ADDRESS, 0x67, 0x18 },

{E_LVDS949_ADDRESS, 0x66, 0x0b },

{E_LVDS949_ADDRESS, 0x67, 0x03 },

/*Set Sync Polarities8 */

{E_LVDS949_ADDRESS, 0x66, 0x0e },

{E_LVDS949_ADDRESS, 0x67, 0x00 },

{E_LVDS949_ADDRESS, 0x66, 0x1A },

{E_LVDS949_ADDRESS, 0x67, 0x03 },

以上

Hi Kailyn,

目前调查发现:是由于内部画面采用的是800MHz内部时钟进行分频导致在HDMI与内部画面无法来回切换

如果内部画面采用是是200MHz内部时钟进行分频,是可以实现HDMI与内部画面来回切换。

为什么内部采用800MHz内部时钟进行分频作为PCLK,在视频Source切换为内部画面时,无法切回内部时钟?

如果要采用800MHz作为内部画面时钟源,在视频Source切换回内部画面需要设定哪些寄存器?

以上

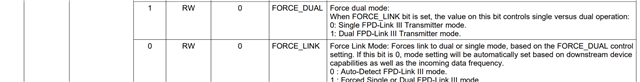

您好,如果采用800Mhz作为内部时钟源,需要配置DUAL_CTL1 0x5B寄存器,配置为force link mode,而不是自动检测模式。如果采用自动检测模式的话,有可能导致检测错误。这个是使用800MHz需要注意的寄存器。您这边再试试。

Hi Kailyn

您好!

0x5B寄存器的bit 5: Reset FPD3 PLL on Frequency Change: When set to a 1, frequency changes detected by the Frequency Detect circuit will result in a reset of the FPD3 PLL. Set to 0.

此bit默认是设置为1.

如果将0x5B设置为0x23时,还是无法从HDMI source切换到内部测试画面Source,

需要将0x5B设置为0x03,才可以实现视频source自由切换。

此bit的作用是什么?设置为0是否OK?会有什么影响?

以上

您好,bit5 =1时指的是,内部频率检测电路检测到的频率变化将被reset。 换句话说,如果配置为1,内部分频配置导致频率变化,是应该被频率检测电路检测到的,但是设置为1之后,会被复位。 配置为0的话,不会对PLL 进行复位。

您好!

如果将0x5B的bit 5设置为1时,无法从HDMI source切换到内部测试画面Source,

需要将0x5B的bit 5设置为0,才可以实现视频source自由切换。

这是什么原因?会有什么影响?

以上

我是这么理解的。

因为内部集成了PLL,我们想要使用的PCLK = M/N*(Oscillator Frequency),这里Oscillator Frequency指的内部晶振频率,为200MHz或800Mhz。M/N指的分频系数。

如果0x5B设置为1,即PLL reset,即是默认值,也就是检测不到频率的变化。

如果设置为0,即按照我们的配置,比如分频系数的配置,能按照上面公式得到我们想要的PCLK。