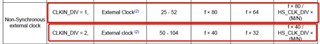

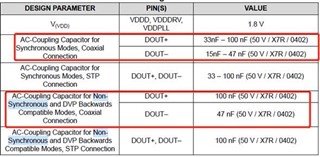

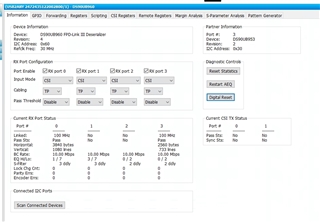

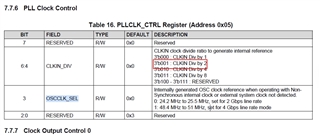

使用 DS90UB953 做视频输出产品,对手件是 964,没有 POC ,两个 serdes 各自单独供电, Synchronous 模式,953 的 CLK 是通过 964 的 FPD-Link 提供。

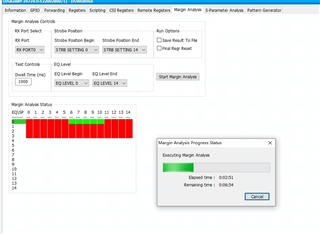

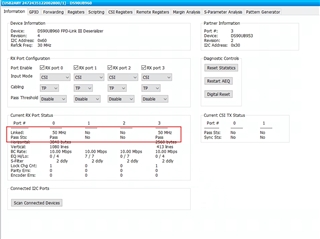

在做低温(-40)实验时,视频输出异常,Link 不上。使用 TI 的 964 demo 测试 FPD-Link ,发现在低温(-40度)时,也是链接不上,link 状态不稳定,断开和连接状态变化。

此时 953 的供电是稳定的。恢复到常温就正常了,线束和其他摄像头是同一套线束,其他摄像头在低温都是正常。不知道这种情况可能是哪里出问题了。