i use DP83867is to connect mac interface with sgmii . i only notice the method to foce the speed to 10M-sgmii with register 0x016f . but how to force the sgmii in 1000M speed .

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

i use DP83867is to connect mac interface with sgmii . i only notice the method to foce the speed to 10M-sgmii with register 0x016f . but how to force the sgmii in 1000M speed .

首先先disable自动协商,然后配置为manual 模式,即force link, 其次就是配置速率。

0x0014 bit7=0 : Disable SGMII Auto-Negotaition.

0x0010 bit10= 1: Force link good according to the selected speed

0x0011 bit[15:14]=10: 1000 Mbps

您好,我在xilinx官网上查到了一款VCU118芯片的demo工程verilog-ethernet/example/VCU118/fpga_1g at master · alexforencich/verilog-ethernet · GitHub,使用的是DP83867IS芯片完成的SGMII。他一共配置三个寄存器如下:

0x31:0x70

0xd3:0x4000

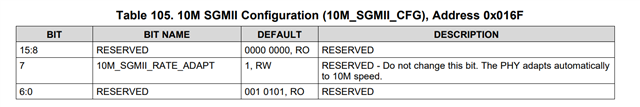

0x16f:0x12

我想请问一下,这种配置对应的应该是SGMII的自协商模式,0x31设置自协商时间持续11ms,0xd3设置sgmii 6线模式

1.如果对端没有设置自协商,而是固定速率,那么在自协商检测时间过去后,phy芯片是会根据在数据中检测到的速率特征信号来确定SGMII速率么?

2.这种设置是怎么确定传输模式为sgmii的,是这三个寄存器中某个有优先级么,只要配置就会识别位sgmii?

3.0x16f按照手册中的描述,配置值0x12应该没有效果啊?

期待您能解答我的疑惑,不胜感激

1.首先如果DP83867 开启的是自动协商,那么对端也需要enable 自动协商。如果像您说的对端是固定速率,我想自动协商时间过后,PHY不会根据在数据中检测到的速率特征信号来确定SGMII速率。

2. 没有优先级。

3. 是的,这个寄存器是不需要配置的。

您好,可以通过strap pin配置,也可以通过寄存器0x0010(PHYCR) bit7=1 enable SGMII来配置。