Other Parts Discussed in Thread: DS90UB947-Q1,

Hi,expert:

问题:DS90UB947-Q1与DS90UB948-Q1联合使用时,显示屏无内容显示。

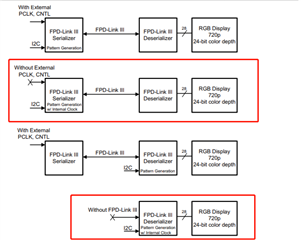

描述:947通过LVDS接口与SOC连接,948通过FPDLINK3与947连接。947部分采用8+2clock信道,modesel_0配置为 1 1;modesel_1配置为 0 1 ;948部分采用8+2clock信道,modesel_0配置为 1 11;modesel_1配置为 1 01;

测试:947到948部分可抓取到信号波形,948到屏幕部分出现时间间隔近似的尖波,屏幕无显示信息。

分析:疑似948的信号处理或模式配置有误,请给予回复,感谢。

Thanks all of that