960 和 Serializer 通信的时候,在不同温度和不同线缆,耐久后,Fpdlink 发送出来的时钟,特别是 Back channel 的时钟在送到 Serializer 时可能有过度的 jitter ,不知道 960 是否有应对的办法,我看到其他家 Serdes 有通过增强同轴线信号输出的电压方式应对这种 Jitter ,一般可以通过修改对应的寄存器可以做到,不知道 960 是否有类似的办法。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

960 和 Serializer 通信的时候,在不同温度和不同线缆,耐久后,Fpdlink 发送出来的时钟,特别是 Back channel 的时钟在送到 Serializer 时可能有过度的 jitter ,不知道 960 是否有应对的办法,我看到其他家 Serdes 有通过增强同轴线信号输出的电压方式应对这种 Jitter ,一般可以通过修改对应的寄存器可以做到,不知道 960 是否有类似的办法。

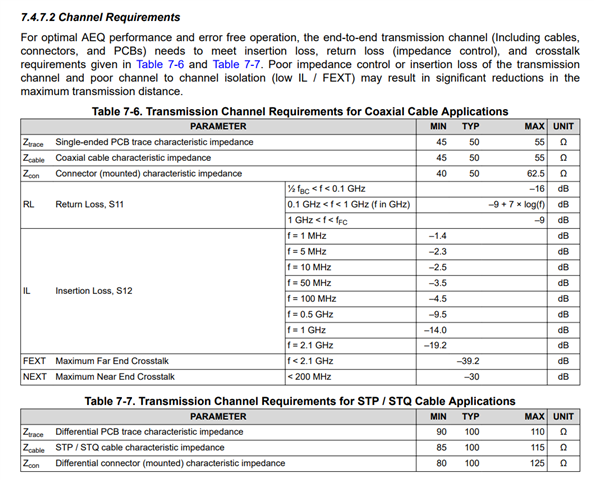

您好,首先960对于coax或者STP cable传输的插值损耗以及回拨损耗的要求如下,cable的插值损耗或者阻抗特性不满足的话会造成信号反射。

960内部也集成了自适应均衡处理AEQ模块,因此不需要去配置EQ的值。 AEQ 过程逐步通过允许的均衡器控制值来查找允许时钟数据的值恢复(CDR)电路、以保持有效的锁定条件。 电路针对每一个EQ的设定等待一个已编程的重新锁定时间周期 。然后,电路会检查结果是否存在有效锁定。 如果检测到有效锁定、电路将停止在当前 EQ 设置下,并在锁定状态持续时保持恒定值。如果是解串器失去锁定,自适应均衡器将恢复锁定算法,EQ 设置将递增至下一个有效状态。 当锁定丢失时,电路将搜索 EQ 设置以查找另一个有效设置,重新采集串行器发送的保持锁定状态的串行数据流。