Hi ,

Two question need your help:

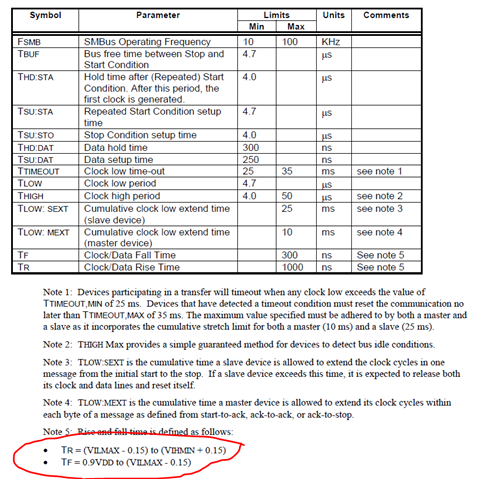

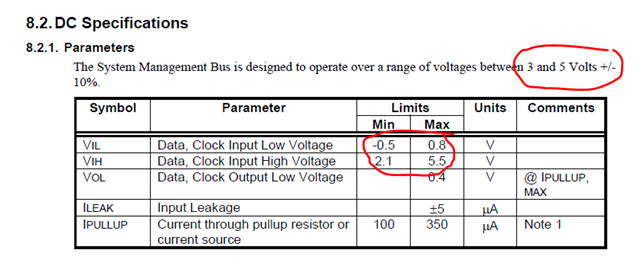

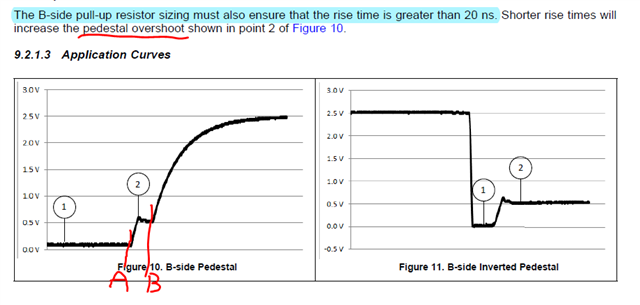

1. What's the start point of IIC signa rise time ? A point or B point in figure 10?

or use the waveform no pedestal overshoot?

2. Usually, signal rise time is 10%--90% stable high level, is this definition also suitable for IIC signal? if not, please give me the corrective IIC signal rise time measure method.

Thanks.