hi everyone:

There are four EDID configurations:

1、We choose the first scheme External local EDID (EEPROM).

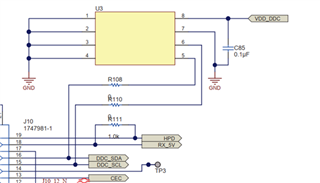

The selected EEPROM chip model is BR24T128-W, the package is DIP-T8, 128K memory (16K*8), 1.6V~5.5V power supply, and the highest frequency of IIC is 400KHZ. Please check with TI to see if it applies.

2、The configuration of MODE_SEL [1:0] is as follows: please confirm whether the configuration is correct

EDID_SEL: 1

AUX_I2S: 0

EXT_CTL: 0

COAX: 0

REM_EDID_LOAD: 0

J10 is an HDMI interface, and now there are the following questions:

1) Whether the 929 chip can read and write the external EEPROM

2) Whether the EDID information in the EEPROM is directly read by the host through the HDMI interface, or is the EDID information in the EERPROM read first through the 929 chip and then sent to the host

3) In what format is the EDID information stored in the EEPROM