Part Number: DP83848J

HI team,

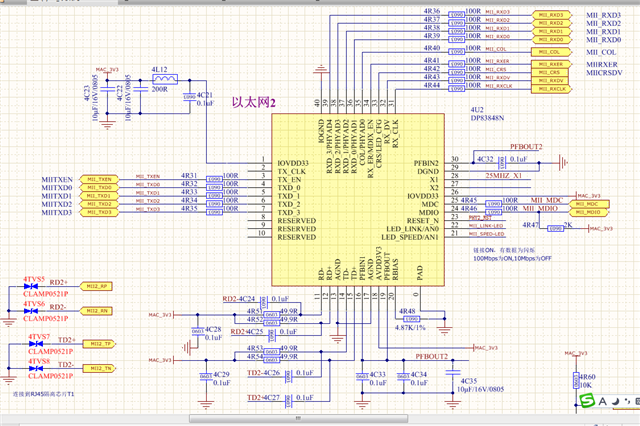

请帮忙建议原理图设计,实际测试中,RMII模式可以连上,但是MII模式连不上。thanks

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,MII连不上,发送端TX_CLK和接收端TX_CLK有输出吗?

TX_EN是否有拉高?MII_MODE是否拉低配置为MII mode?

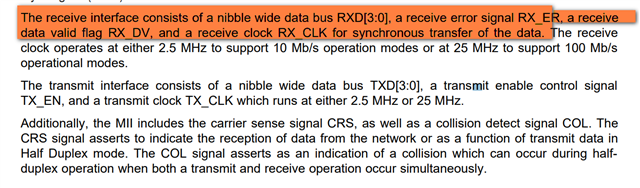

RST是直接拉高了还是通过GPIO控制了它的上电时序?RX_ER输出什么电平?如下描述,如果接收端有接收错误的话,RX_ER会拉高报错(100Mbps)。

发送端是否有有效的数据输入到TXD?

意思是MII模式只能从TX_CLK脚输出的25MHz时钟,不能从晶体输出提供给MAC吗?

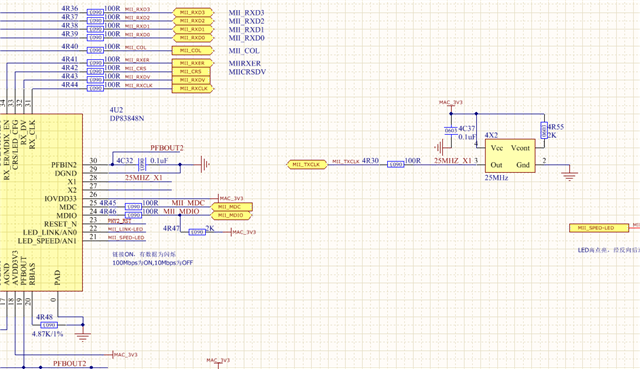

晶体输入作为参考时钟,TX_CLK是通过DP83848内部分频电路产生25Mhz 输出(100Mbps)或2.5Mbps(10Mbps mode)。

将TX_CLK输出连接MAC的TX_CLK,终端插入网线后,DP83848N还是没有反应,

TX_CLK能正常输出吗?

LINK、SPEED两个LED一直常亮。

常亮代表已经link上了呢,LED_SPEED常亮代表100Mbps 模式下i已经link上,既然已经link上,TX_CLK是否正常输出25Mhz?

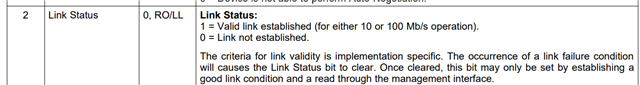

另外,寄存器0x01 bit2也可以监测是否已经正常link。如果读取为1, link已经建立,说明PHY初始化正常。

hi kailyn,

1、MII连不上,发送端TX_CLK和接收端TX_CLK有输出吗?

TX_CLK无输出

2、TX_EN是否有拉高?MII_MODE是否拉低配置为MII mode?

TX_EN 为低 MII_MODE 有上拉;为高

3、RST是直接拉高了还是通过GPIO控制了它的上电时序?RX_ER输出什么电平?如下描述,如果接收端有接收错误的话,RX_ER会拉高报错(100Mbps)。

RST 是直接拦RC 拉高,没有通过GPIO控制,

RX_ER 是高电平

4、发送端是否有有效的数据输入到TXD?

TX_CLK无输出

TX_CLK 无输出,说明PHY内部的clock gen没有正常工作。

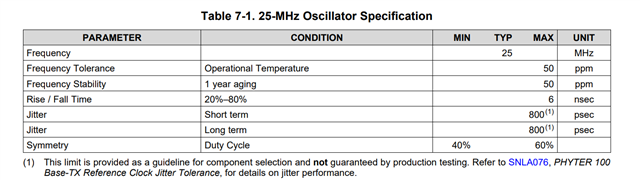

25Mhz的晶振是否满足MII mode下的要求? MII模式使用25Mhz的参考时钟,RGMII使用的是50MHz的时钟,我看电路您这里确实是使用的25Mhz晶振。能否换一下其他25MHz的时钟试试?比如CMOS有源晶振试试呢?

原理图的话可以直接参考EVM user‘s guide:

https://www.ti.com/lit/df/snlr019/snlr019.pdf

另外,这个波形是25Mhz的时钟信号吗?看起来像是正弦波,时钟信号应该是类似于削波的正弦波。

你这个波形满足rise/fall time要求吗?