我司方案设计 ,主与从单板上两FPGA走背板通过serdes通讯(2.5G bps);背板上走线长约3000mil ;

现在在接收端测试,信号眼图很差,经常通道连接不上;

请教TI有推荐的解决背板高速串行信号通讯问题的器件或方案吗?

感谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我司方案设计 ,主与从单板上两FPGA走背板通过serdes通讯(2.5G bps);背板上走线长约3000mil ;

现在在接收端测试,信号眼图很差,经常通道连接不上;

请教TI有推荐的解决背板高速串行信号通讯问题的器件或方案吗?

感谢

您好,根据您的介绍,可以参考DS100KR401这类高速redriver(10.3Gbps)并且可以支持背板应用。 您参考下它的数据手册看是否满足您的应用需求:

感谢您的及时回复,根据IT的评估板方案:

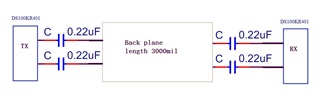

我在主从两个单上各加一个redriver DS100KR401,如下图,serdes差分对在背板上的长度约3000mil ; 两个单上的DS100KR401在TX与RX都要加AC 耦合的电容吗?谢谢

您好,DS100KR401 输入是CML电平,AC耦合的目的是将原来的直流共模电压隔离掉,然后重新建立新的共模电压。如果transmitter输出的电平和receiver的输入电平是相同的,比如都是CML电平,可直接DC耦合。