SN65LV1224B 的输出RCLK是不是与REFCLK频率,时序是相同的? 我写verilog代码的时候感觉不能用RCLK做逻辑时序的always判断,就想问下是不是可以用REFCLK?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

SN65LV1224B 的输出RCLK是不是与REFCLK频率,时序是相同的? 我写verilog代码的时候感觉不能用RCLK做逻辑时序的always判断,就想问下是不是可以用REFCLK?

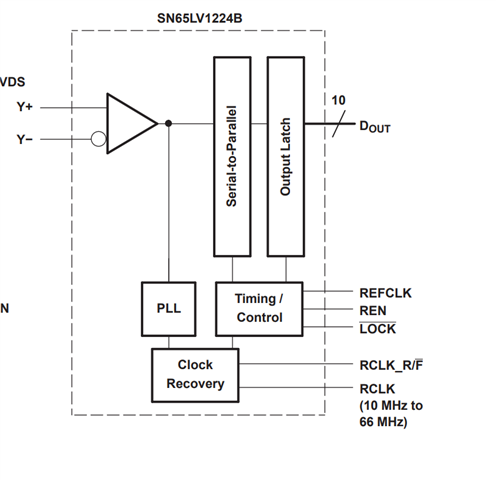

您好,REFCLK是内部PLL的参考时钟,而RCLK是恢复时钟,是用来选通输出数据Dout的时钟信号。

RCLK和REFCLK频率相同,但是由于RCLK是PLL经过clock recovery 模块输出的时钟,所以相位有一定的延迟。

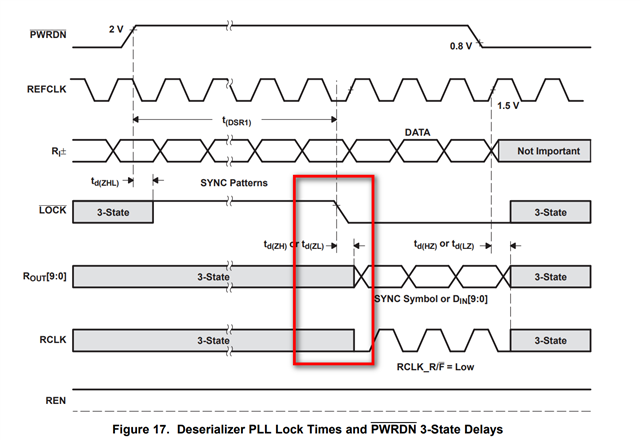

或者rclk比lock信号晚几个时钟变成1'bz,也能写代码啊,看时序图lock与rclk时同步变成1‘bz的,那用verilog就没法采样了啊。

我看 “数据传输模式 DATA TRANSMISSION MODE” 里面也没有提,是不是 PWRDN和REN都为高的时候,RCLK就一直有效?

那就是不能用REFCLK来锁定数据了吗?

REFCLK 只是一个参考时钟来帮助解串器 PLL 实现锁定,lock之后,ROUT才会在RCLK的上升沿或下降沿输出有效数据。

或者rclk比lock信号晚几个时钟变成1'bz,也能写代码啊

所以您可以从时序中看到,LOCK和RCLK之间是有一个delay的。这个delay就是FIgure 13的td(ZH)或td(ZL)。

数据传输模式 DATA TRANSMISSION MODE” 里面也没有提,是不是 PWRDN和REN都为高的时候,RCLK就一直有效?

不是,只有当内部PLL lock之后,recovery clock RCLK才会有输出。

那内部pll锁定之后,RCLK是不是就不变化了,,我理解的是数据通过1023发过来,当1224的LOCK输出低,RCLK正常,一帧数据接收完,RCLK还是稳定的,LOCK输出高,这样就能判断一帧数据结束了。下一帧数据过来,LOCK输出低,RCLK继续正常,这样才能一直不间断的接收,这样对吗?

一帧数据接收完,RCLK还是稳定的,LOCK输出高,这样就能判断一帧数据结束了。

应该是一帧数据接收完之后,lock为高,RCLK为高阻态。

时钟RCLK变成高阻态,我还不知道fpga怎么处理接收数据了,有没有人用fpga采样过1224接收的数据,指导下。

抱歉,关于FPGA如何处理接收数据,建议您登录英文E2E 可以咨询下我们的美国工程师:

https://e2e.ti.com/support/interface-group/interface/f/interface-forum