我在PCA9306规格书中看到有关于此芯片能够隔离I2C容抗,并起到允许延长走线的目的,请问它是如何实现的呢?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,这里描述的意思是这样的: 因为I2C协议规定I2C 的最大负载不能超过400pF。

我们知道tracei越长,容性负载越大,因此400pF的容性负载限制了trace的长度。

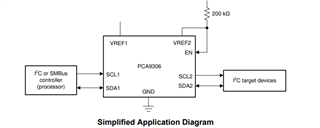

而使用PCA9306,则会放在 I2C的节点与节点之间(或者两个节点中间),相当于PCA9306在中间做了个隔离,这样以来本来I2C device1和device 2之间的400pF限制的trace长度变为device 1和PCA9306的trace有400pF的限制,PCA9306和device 2之间trace有400pF的限制,即为上述描述的trace长度延长了。

实际测试I2C容抗时,并不会对PCA9306 EN脚去拉低,也就是说实际测试时PCA9306的管子也会处于导通状态,并不能起到隔离的作用吧?

没有关系,这里的隔离实际是对trace的隔离,换句话说,比如受到400pF的限制左边device 1本来只能驱动到device 2的trace 长度。 加了PCA9306之后,device 1能驱动的长度则减小到device1到PCA9306的距离,9306驱动的长度再重新受到400pF的限制,这样以来,trace的长度是不是就增加了。

也就是说它实际上是通过改善驱动能力来达到延长trace和允许更大电容限制的作用,并不是真正起隔离作用是吧? 从端口测试容抗并不会减小实际测到的容抗值,而是把它的限制范围加大了,比如之前允许400pF,增加PCA9306后全段走线可能能允许600~800pF,但实际依旧无法满足协议要求的指标,这样理解对吗?

应该是满足协议要求的,这段 描述的意思应该是理解为400pF的容性负载限制是节点和节点之间的距离。

但是我看了下这款器件的数据手册,这段介绍已经没了,您是参考的最新版本的数据手册吗?

https://www.ti.com/lit/ds/symlink/pca9306.pdf

另外,更正下,PCA9306没有重驱动能力的,看下它的工作原理,它仅允许低电平信号在1侧和2侧之间导通。因此,关于I2C总线电容的理解,我们需要确保 主控电容,IO 扩展器电容和 PCB 寄生电容的一共要低于400pF 的总限制。

PCA9306没有重驱动能力,所以在测试容抗过程中,低电平导通时,测到的容抗应该就会包含PCA9306后端的PCB走线容抗,所以我们应该如何来评估这种情况呢?

您好,您的意思是如何测量知道是否超过400pF负载是吗?

首先影响I2C信号的rise time,上升速度应该是减慢的,解决方法就是可以降低上拉电阻值,提高上升沿速度。

但是这样势必也会额外增加Icc电流,增加功耗。