Part Number: DS90UB948-Q1

查看948的LOCK状态(0x1c寄存器的bit0和bit1)为1,即说明解串出了有效的视频信号,但是LCD还是无画面。

所以想确认下解串后的视频信号的timing是否符合LCD的要求,是否有相关寄存器可以读呢?

Thanks!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS90UB948-Q1

查看948的LOCK状态(0x1c寄存器的bit0和bit1)为1,即说明解串出了有效的视频信号,但是LCD还是无画面。

所以想确认下解串后的视频信号的timing是否符合LCD的要求,是否有相关寄存器可以读呢?

Thanks!

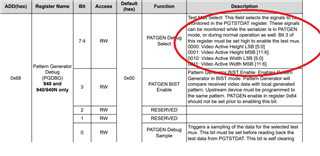

您好,您是使用的internal pattern显示吗?如果是的话,948可通过0x68寄存器进行回读:

如果不是使用内部pattern,建议按照这篇应用手册的配置,先使用内部pattern 进行debug,看是否能显示。

https://www.ti.com/lit/an/snla132g/snla132g.pdf

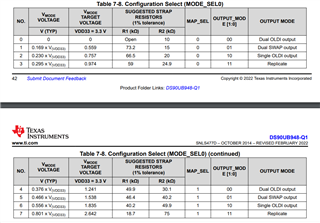

您好,VESA还是JEIDA格式,是由MODE_SEL[0]这个strap pin决定的,所以您看下电路中这两个引脚的上下拉阻值为多少?然后对照tTable7-8 去确认是VESA还是JEIDA格式。

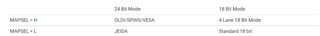

mapping是由MAPSEL的高低电平决定的,mapping如下:

您好,应用图示中941输出的是只使用的DOUT0这一组FPD link output是吗?那941就配置signle link。

single link和dual link指的是FPD link。

而对于948来说,同样,1 lane FPD link input,但是输出两路LVDS,即配置为1 lane input, dual link output。 参考948数据手册的7.4.1

1080p60hz需要的像素时钟是148.5MHz,所以是的,941应该配置成为dual link 模式。