Part Number: DS90UB941AS-Q1

串行器使用941,解串器948。在941上配置test pattern color bar,使用内部timing、内部时钟:

i2cset -f -y 2 0x0c 0x65 0x04 b // 使用Pattern Generator 内部timing

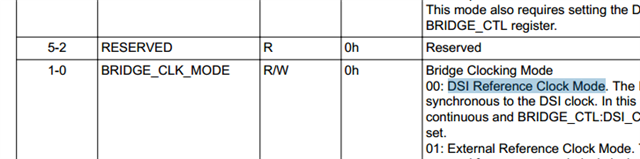

i2cset -f -y 2 0x0c 0x56 0x02 b // 使用Internal Reference Clock

此时948输出正常,LCD能正常显示color bar画面。

1、在上面的基础上,将0x56寄存器改为0x00,即使用外部DSI输入给941的时钟,color bar也能正常显示。

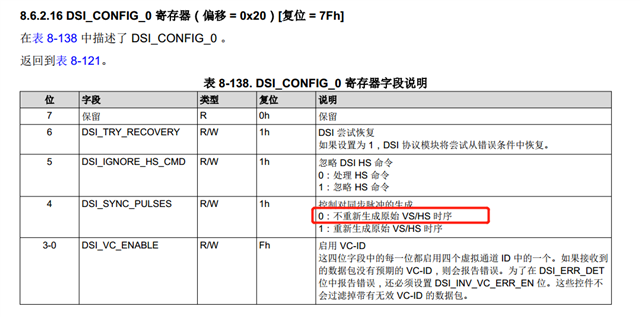

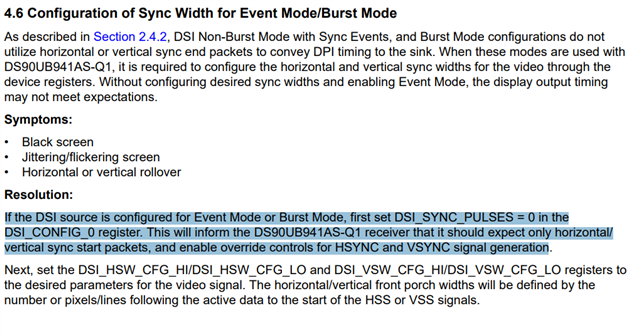

2、在1的基础上,将0x65寄存器改为0x00,即使用外部DSI的timing,color bar不能显示!!!

看起来问题出在外部DSI的timing上面,但是我们在SOC的MIPI DSI配置的timing参数和在941上PG配置的是一致的。

也就是说,941在PG模式产生的timing屏可以正常工作,而从DSI输入中解析出来的timing无法驱动屏正常工作。请协助分析,提供排查方向。

Thanks!