Other Parts Discussed in Thread: DS90UB941AS-Q1

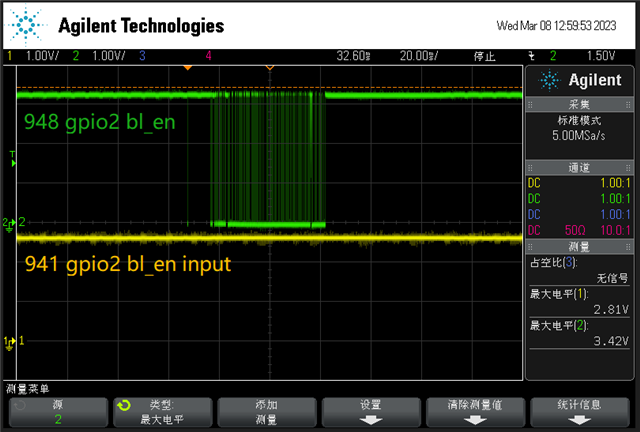

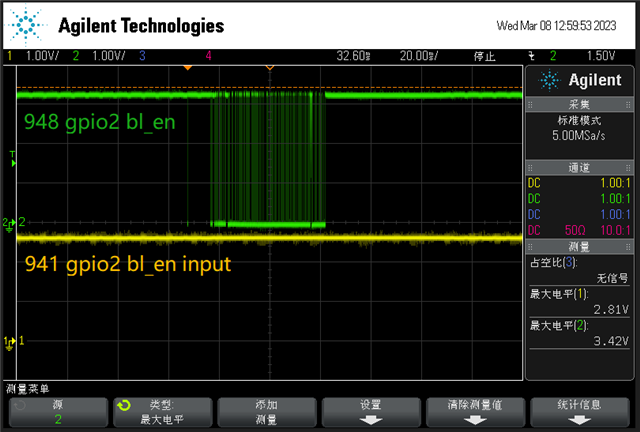

现象为屏幕不定时的闪黑屏。通过抓取948的GPIO2(BackLight_EN)发现,闪黑屏时信号异常,见下图:

同时测量了串行端941的GPIO2的输入信号是稳定的。

941的0x0e寄存器配置为0x3f

948的0x1e,寄存器配置为0x53

请帮忙分析,Thanks!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

现象为屏幕不定时的闪黑屏。通过抓取948的GPIO2(BackLight_EN)发现,闪黑屏时信号异常,见下图:

同时测量了串行端941的GPIO2的输入信号是稳定的。

941的0x0e寄存器配置为0x3f

948的0x1e,寄存器配置为0x53

请帮忙分析,Thanks!

您好,为更加有效地解决您的问题,我已将您的问题发布在E2E英文技术论坛上,请资深的英文论坛工程师为您提供帮助:

英文工程师的回复:

您能提供在SER和DES上连接GPIO2的原理图吗?

此外,请提供您正在为这些GPIO应用的配置;

此外,LOCK何时或为什么变得不稳定?有什么特殊条件吗

can you provide schematics how are you connecting GPIO2 on the SER and on the DES?

Also please provide which configurations are you applying for those GPIOs?

Additionally, when or why is LOCK getting unstable? Any special condition?

分辨率:1920x1080

帧率:60Hz

消隐:hsw=44,hbp=148,hfp=88;vsw=5,vbp=36,vfp=4;

hblank=44+148+88=280;vblank=5+36+4=45;

htotal=1920+280=2200;vtotal=1080+45=1125;

pclk:2200*1125*60=148.5MHz

FPD-LINK:Dual link mode

串行器:DS90UB941

串行器PG测试:当使用内部时钟(0x56寄存器设置为0x02)、PG自己产生的timing(0x65寄存器设置为0x04)时,没有问题,test pattern显示是稳定的;

当0x56=0x02(内部参考时钟模式)时:

0x65=00 (外部timing):黑屏无显示;

0x65=04 (内部timing、内部分频时钟):稳定不闪;

0x65=0C(内部timing、外部像素时钟): 黑屏无显示;=======> 我们并没有给941外接参考时钟。

当0x56=0x00(DSI 参考时钟模式)时:

0x65=00 (外部timing):有显示但会闪;

0x65=04 (内部timing、内部分频时钟):稳定不闪;

0x65=0C (内部timing、外部像素时钟):有显示但会闪;

从上面来看:

1)当0x65=0x04时,不论0x56如何配置,都稳定不闪。

2)当0x56=00 即参考时钟选择DSI时,无论0x65=00或者0C,都会闪屏。这应该都能说明是是DSI时钟的问题吧?