Part Number: TCAN4550-Q1

你好:

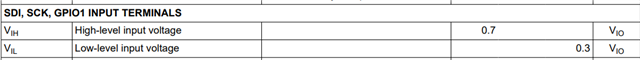

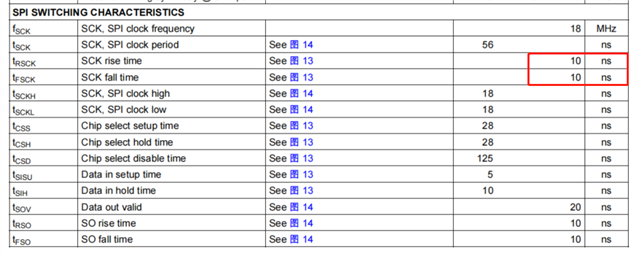

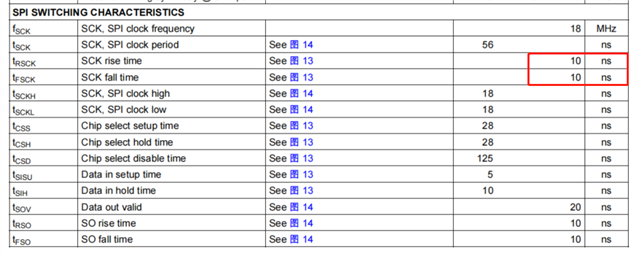

SPI clock frequency 最大可到18MHz,并且规格书要求SCK rise time和SCK fall time小于10ns,对于通讯速率只有3MHz的应用,这个上升时间和下降时间实测为35ns,这是否满足通讯要求,要如何改善这个问题。

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TCAN4550-Q1

你好:

SPI clock frequency 最大可到18MHz,并且规格书要求SCK rise time和SCK fall time小于10ns,对于通讯速率只有3MHz的应用,这个上升时间和下降时间实测为35ns,这是否满足通讯要求,要如何改善这个问题。

谢谢。

您好,需要满足datasheet中的SPI时钟的上升沿和下降沿要求。

SPI时钟的上升沿和下降沿取决于MCU。您测下来35ns,是测试的上升沿30%~70%的区间吗?

您好,测试的是10%~90%的区间,请问规格要求的是30%~70%区间吗

是的,clock的rise /fall time 是基于30%~70%区间。因为您看它的高低电平阈值分别时0.3和0.7Vio。并且通过波形来看,应该也是30%~70%的区间。

但是注意SDI采样和SDO输出数据都是在时钟的低边沿到高边沿或者高边沿到低边沿的区间。