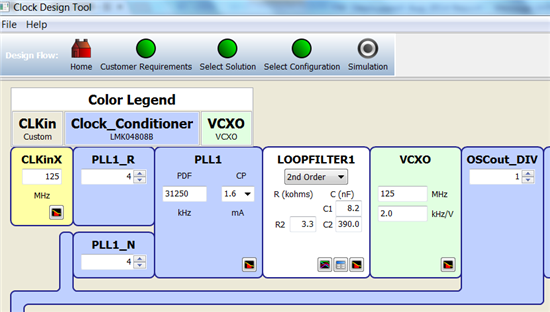

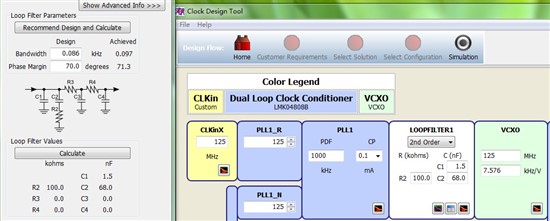

目前系统中使用1片lmk04808,

输入时钟频率:125M;

VCXO频率:125M;

PLL1相关配置参数为参考设计给定值:

Mode:Dual PLL, Internal VCO;

PLL1_WND_SIZE : "11";(40ns)

PLL1_DLD_CNT:0x400(1024)

PLL1的外部环路滤波器参数是参考设计给定的为:

C1:0.1uF;C2:0.68uF;R1:39K;

问题:在上电配置完成后,发现PLL1不是每次都会锁定,即在配置相同的情况下,有时上电可以锁定,有时无法锁定(通过PLL1_DLD引脚观察),这是为什么?(PLL2始终可以锁定)