各位论坛里的高手:

大家好!

公司最近一个项目上用到了CDCE62005这个芯片,在调试的过程中遇到了PLL不能正常锁定的情况。

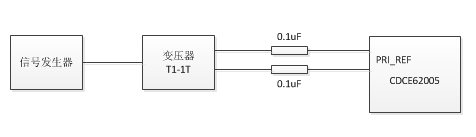

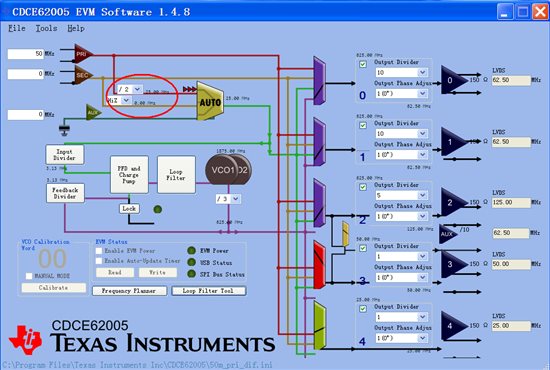

板子上CDCE62005的原理框图如下:

参考时钟是来自于别的模块,在调试过程中暂时用信号发生器来代替了。

我的调试过程大概如下:

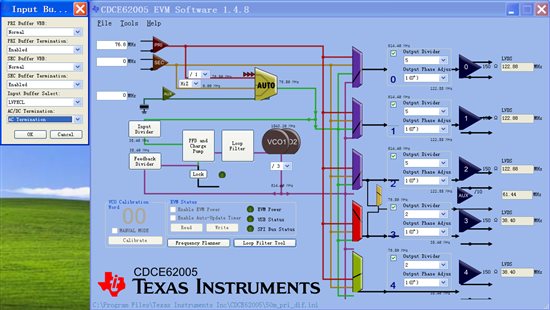

1、我自己的板子上实际的输入和输出设置如下:

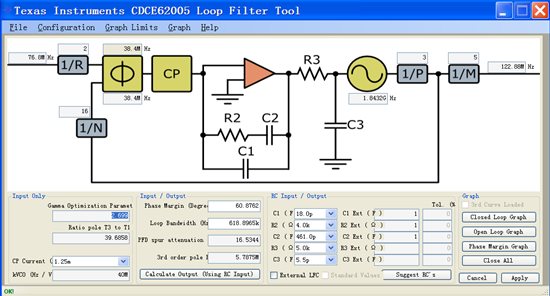

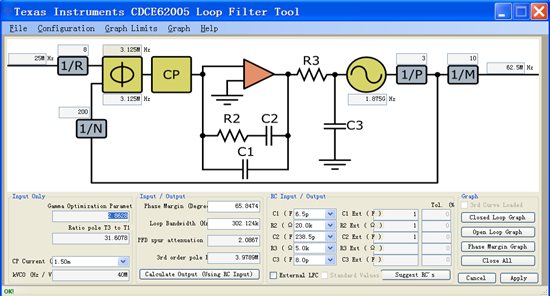

环路滤波器的设置如下:

软件生成的寄存器值如下:

REGISTERS

0 EB860320

1 EB860301

2 EB860302

3 EB800003

4 EB800114

5 18040BE5

6 149E0126

7 BD91FDE7

8 80001808

把这个配置写入到CDCE62005之后,发现PLL_LOCK信号经常失锁,就像一个时钟信号一样,然后测量输出通道0~2为111MHz,而通道3~4为38.4MHz,通过这一现象,说明PRI的输入时钟已经被input buffer识别了,且经过Multiplexer之后都还正确的,但是进过VCO之后再分频出来的时钟就不正确了。

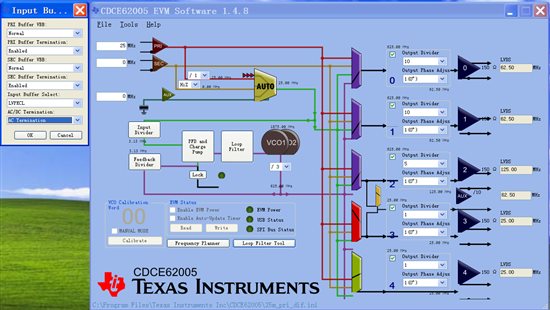

接下来我做了一个实验,将输入和输出配置成如下:

环路滤波器设置如下:

然后将软件生成的寄存器值写入到CDCE62005中,PLL正常锁定,且每个通道的输出均是正确的。

再接下来我将输入时钟改为50MHz,将PRI_REF的预分频设置为2,其他配置和以25MHz输入一直,如下图所示:

然后将软件生成的寄存器值写入到CDCE62005,这时候奇怪的事情发生了,PLL完全失锁,然而通道3~4有输出且为25MHz。

通过以上的实验发现PFD和VCO等的配置及输入完全没有改变,只是改变了PRI_REF输入端口的信号,为什么PLL就完全失锁了,这个到底和什么有关系?请给位高手指点一下,接下来我应该怎么调试这个电路?