Other Parts Discussed in Thread: SN74HCT244, SN74ABT16244A, SN74LVTH16245A

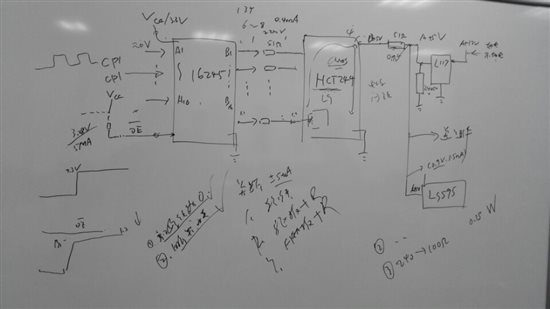

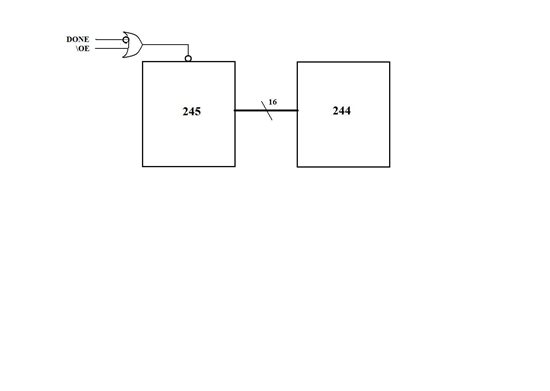

在设计中我们用FPGA驱动探测器。SN74LVTH16245用在FPGA板上,SN74HCT244用在探测器板上,分别作为信号缓冲器,两者之间信号用51Ω电阻隔开。如下图示。

FPGA板先上电,探测器板后上电。FPGA采用Xilinx的VirtexII Pro,采用Master Serial配置方式,上电配置时间约3秒,FPGA板上的SN74LVTH16245的\OE端未连接一个上拉电阻至VCC,由FPGA输出的信号控制,因此在FPGA配置的3秒时间内未能有效将SN74LVTH16245置于3态输出。此时,探测器板未上电,板上的SN74HCT244接收到SN74LVTH16245的输出信号。请问会有什么影响和后果?谢谢!