Part Number: DS90UB941AS-Q1

Other Parts Discussed in Thread: SN65DSI83

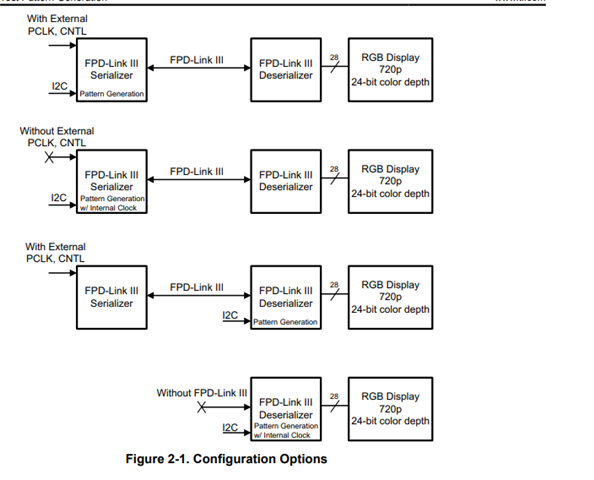

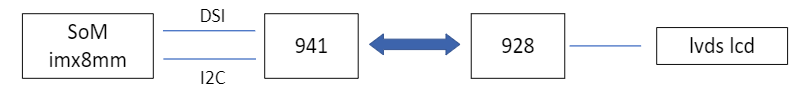

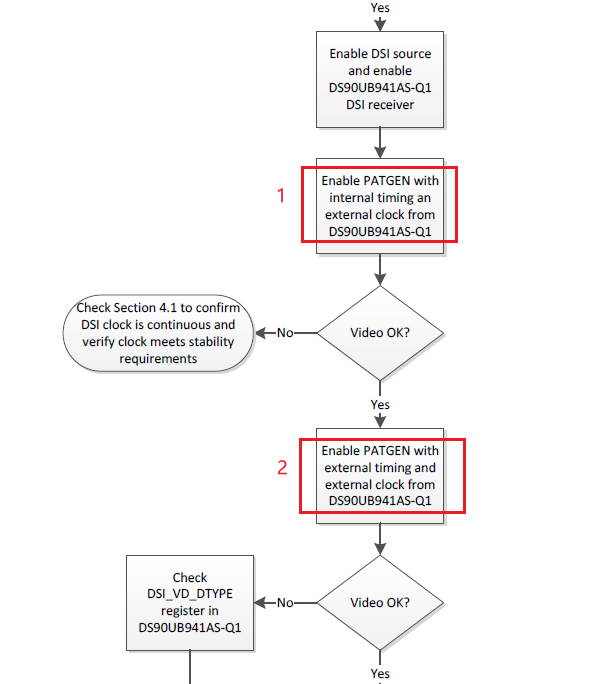

您好,前两天我们使用内部时钟和内部时序的图形生成器点亮了屏幕,应用简图如下:

然后按照启动指南手册里的:

1 下一步需要使用DSI 时钟和内部时序来使能图形生成器。

2 如果ok,那么再下一步需要使用DSI 时钟和DSI timing来使能图形生成器

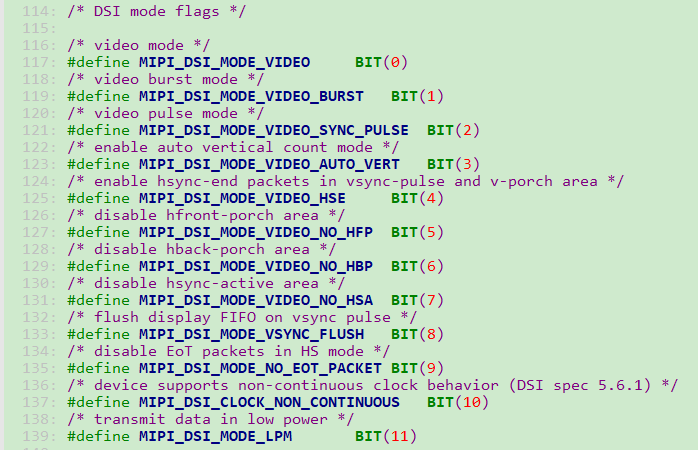

我们将MIPI DSI源配置为视频模式,突发模式,连续时钟模式

-------------------------------------------------------------------------------------------

对于寄存器的配置有些不确定的地方:

1. 使用DSI 时钟和内部时序这一步相对于内部时钟、内部时序图形生成器的寄存器配置,是不是仅需要将寄存器0x65的bit3 设为1就行了?还需要其他设置吗?

2. 再下一步使用DSI 时钟和DSI timing是不是也仅需要将寄存器0x65的bit2 设为0?还需要其他设置吗?

谢谢!