Other Parts Discussed in Thread: ALP, DS90UB941AS-Q1

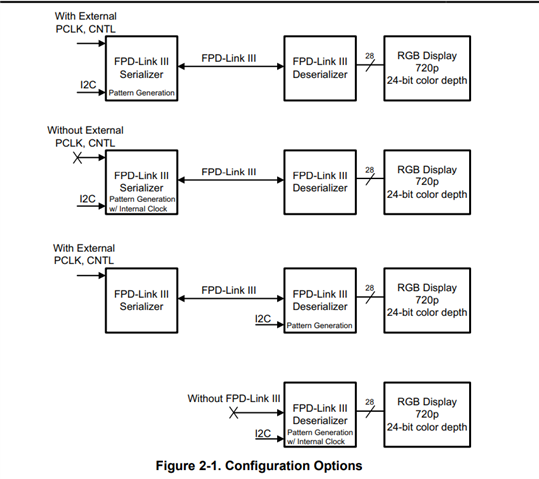

配置

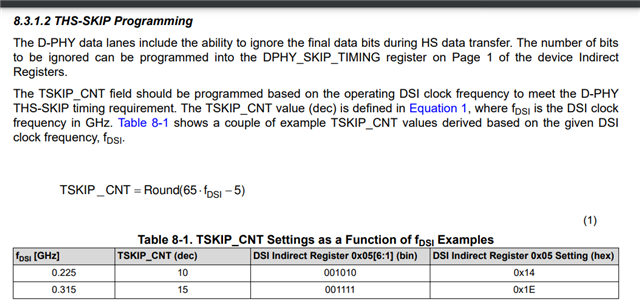

MIPI / SYNC_PULSE_VDO_MOD -> 941 -> cable -> 948 -> LVDS / DE

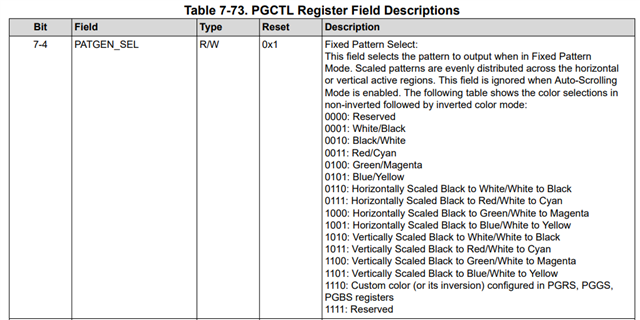

使用APL時 Eanble PGEN / Timing Source:Externel 無畫面

DSI_VC_DTYPE為0

想請問在這樣的架構下941/948是否有其他需設置的Register?

或是有什麼其他排查的方向

MIPI SOURCE

- data lane每帧回LP11(Low Power state,dp,dn都为高电平),clk一直HS( High Speed),对应配置:

- params->dsi.cont_clock=1;

- params->dsi.clk_lp_per_line_enable=0;

.png)