Part Number: SN65CML100

Other Parts Discussed in Thread: TLV3801

在我们的系统中有一块板子设计用来处理高速脉冲信号,电路涵盖了前端SiPM探测器,共基极放大、隔离放大以及关键的高速比较器电路(使用TI的TLV3801)。由于单板处理多通道,故多路比较器得到高速脉冲后经过高速逻辑器件合并成单路脉冲信号输出。所以,整个电路由于涉及到各家各种不同高速器件,可能每家输入输出端口的差分标准各异,这就涉及到了各种不同差分标准接口之间互联问题。为了,尽可能保留高速脉冲的上升沿信息,电路中差分互联均采样了AC耦合设计。(注:本系统产生的脉冲信号都是随机偶发单脉冲,没有任何周期规律或占空比指标要求。)

这种AC耦合互联问题出现在了下述3种情况:

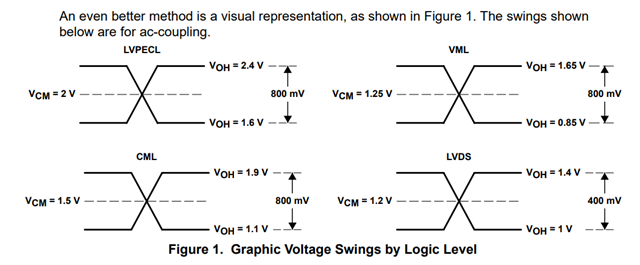

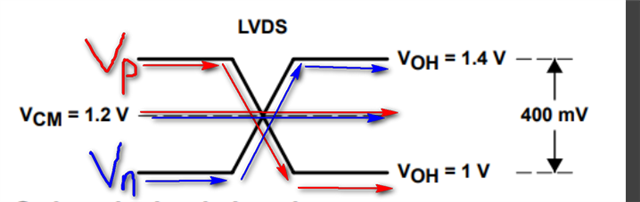

1、LVDS作为驱动(driver),CML作为接收(receiver)。这个问题单独开贴已与TI对应产品工程师沟通。

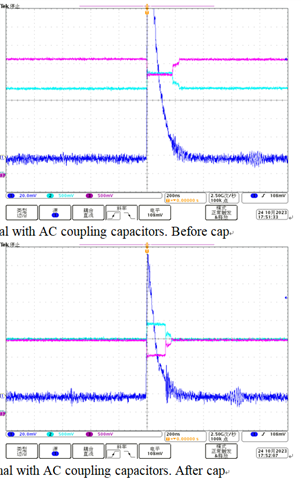

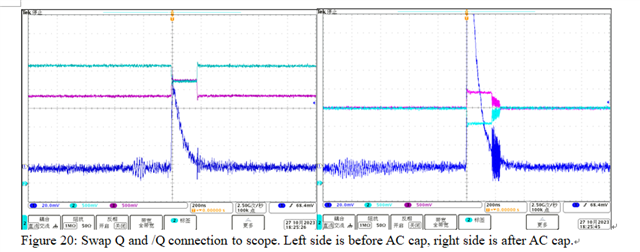

2、CML作为驱动(driver),CML作为接收(receiver)。示波器通道1是为比较器输入信号,该信号与比较器预设的阈值比较获得方波单脉冲输出。该脉冲在传输过程中,CML驱动CML时候AC耦合电容前后测量得到的信号如下图所示,示波器通道2和3分别测量差分对P/N。

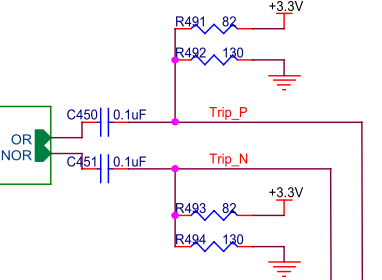

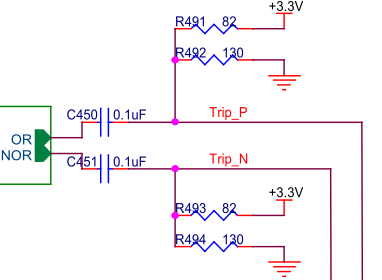

3、CML作为驱动(driver),LVPECL作为接收(receiver)。该脉冲在传输过程中,CML驱动LVPECL时候AC耦合电容前后测量得到的信号如下图所示,示波器通道2和3分别测量差分对P/N。下图右侧是CML输出到LVPECL接收的原理图,AC耦合电容后油82ohm和130ohm电阻网络对隔直后的信号进行重新偏置以匹配后级LVPECL输入端口。

我们的问题是:不管是CML驱动CML还是CML驱动LVPECL为何AC耦合电容前后测量得到的差分信号均表现异常?