Part Number: DS90UB941AS-Q1

Other Parts Discussed in Thread: ALP

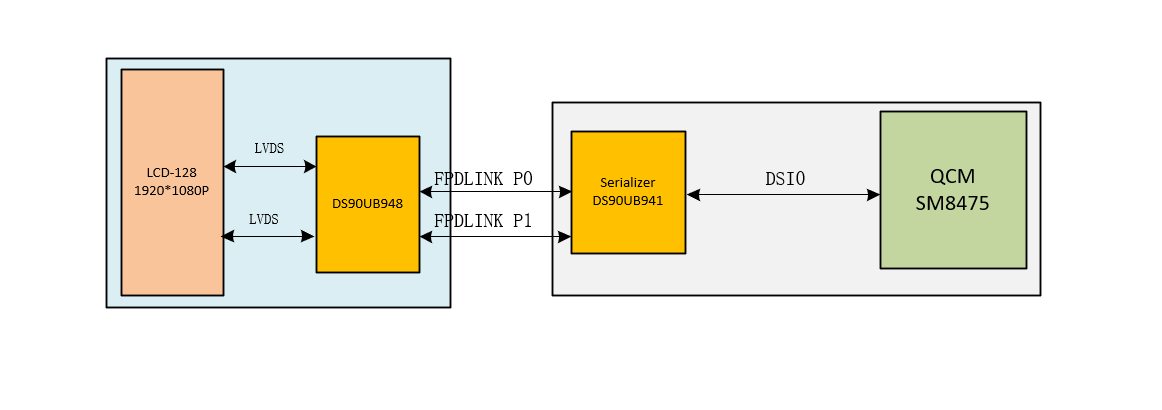

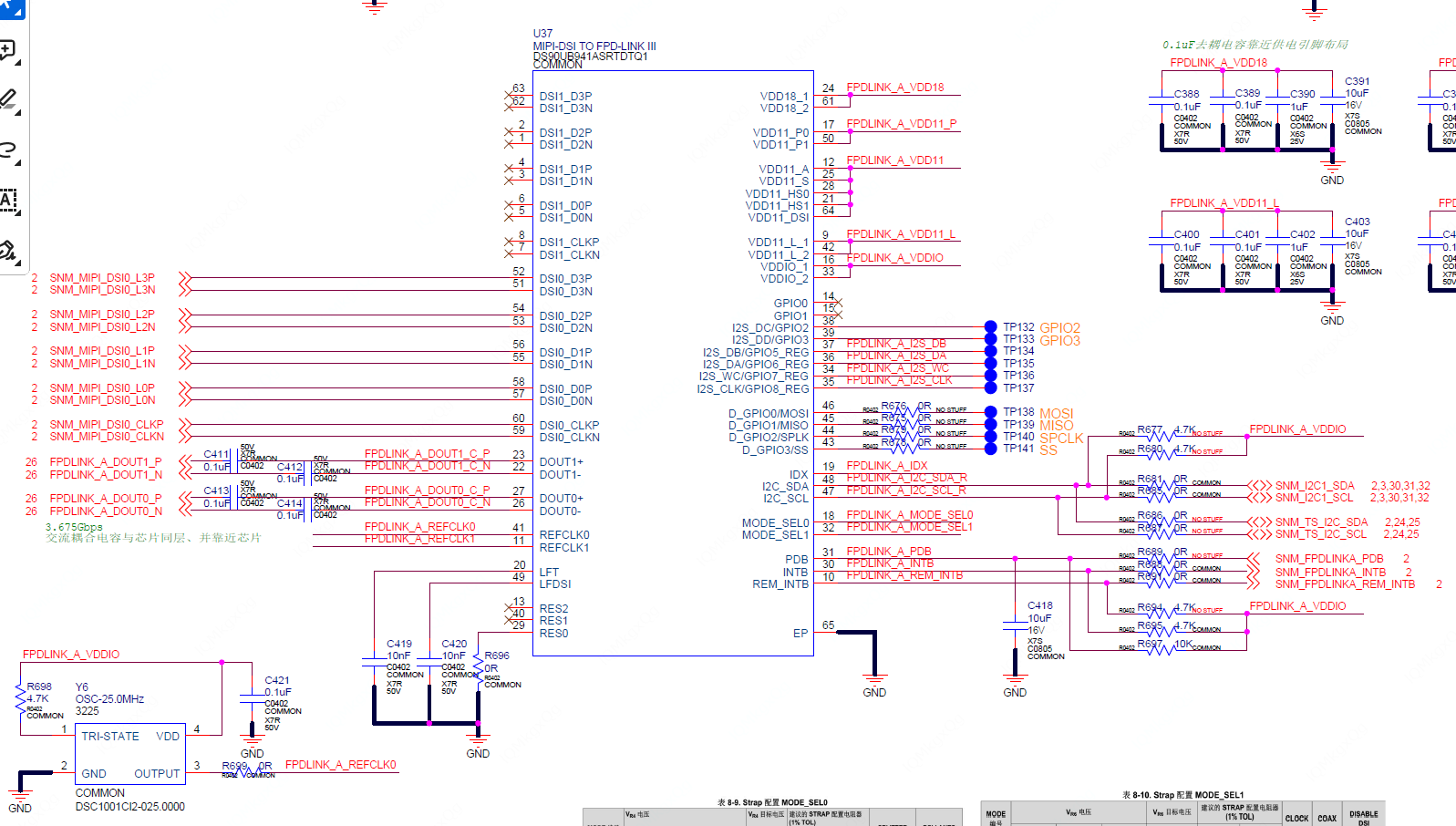

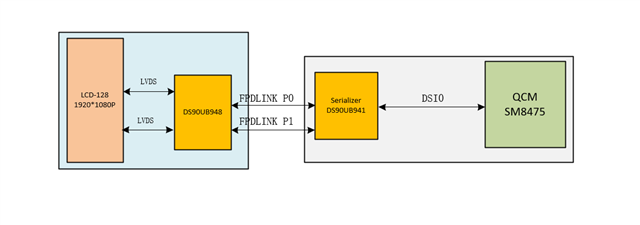

Our 941 application is shown in the following figure, using one DSI0 output to 941 ,941output two FPDLINK to 948,948 output two LVDS with a resolution of 1920* 1080P@60Hz Display screen.

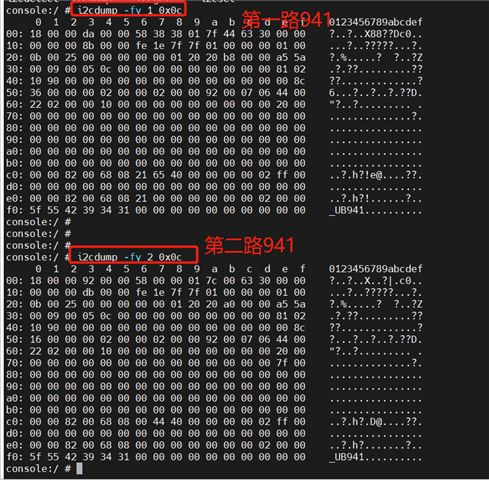

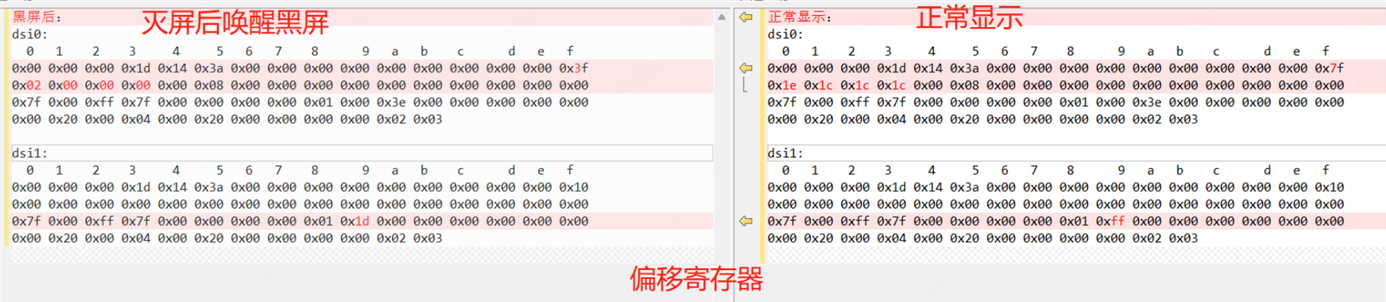

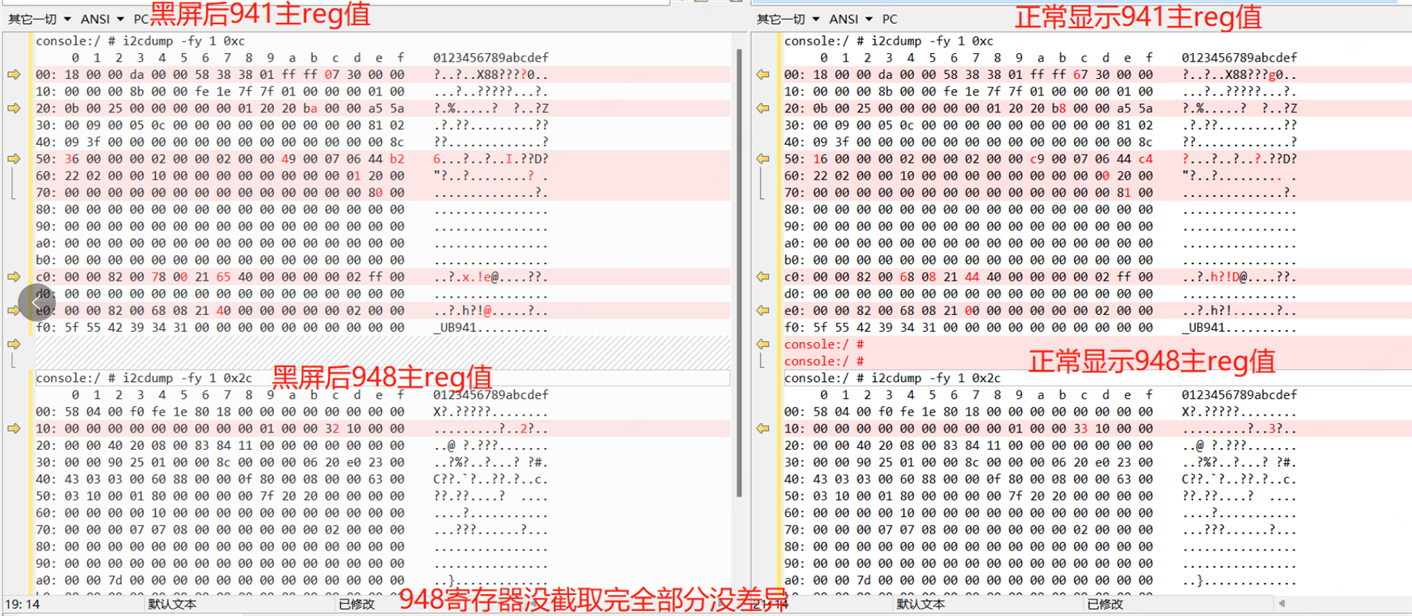

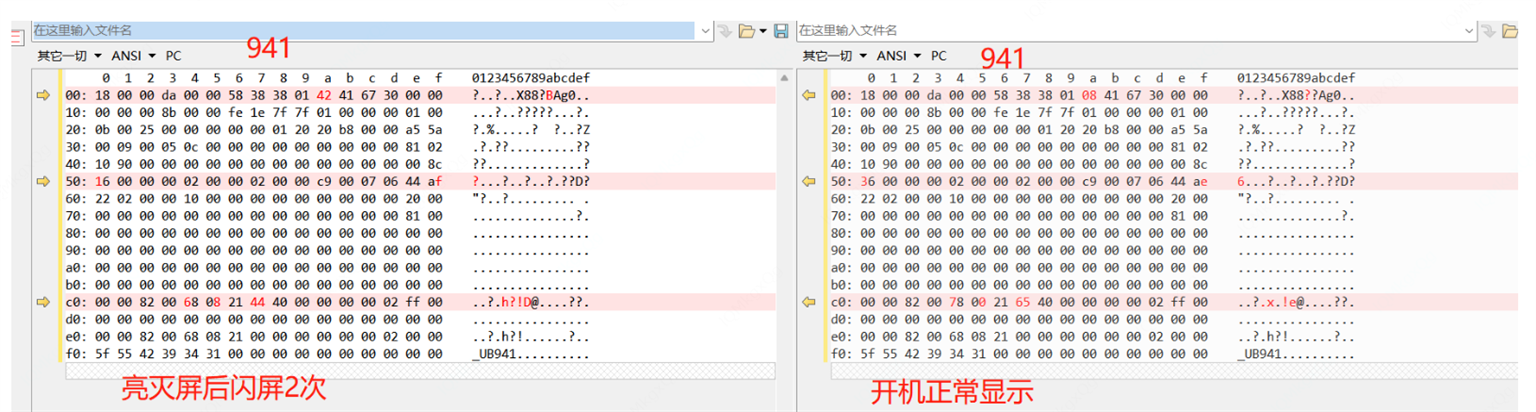

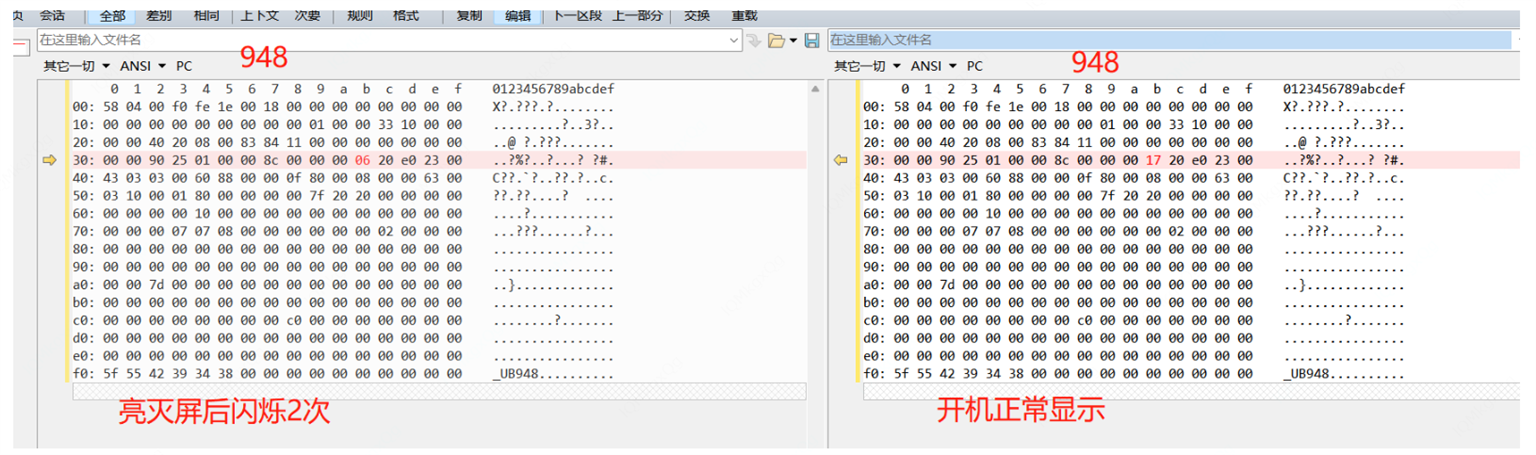

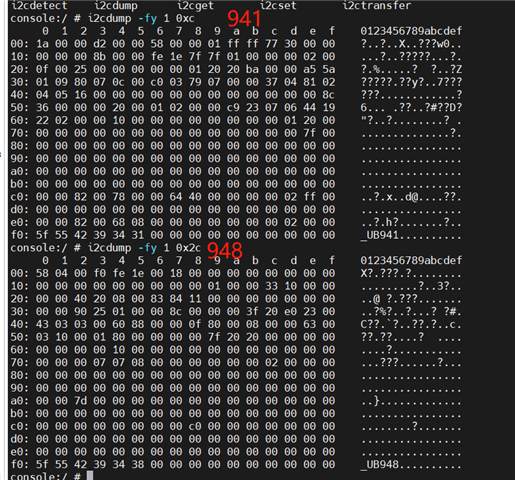

The I2C register configurations for 941 and 948 are as follows:

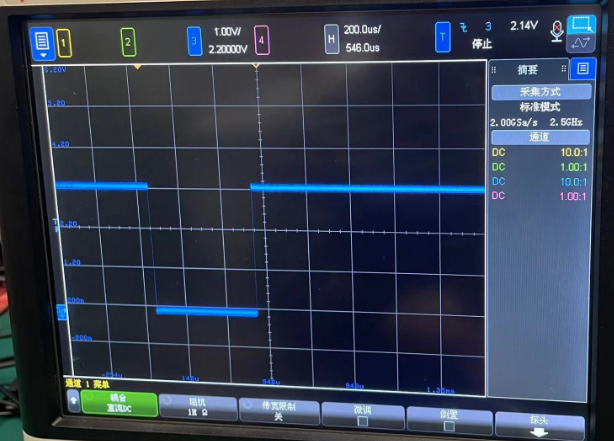

The current problem is that the display screen is blurry and flickering. Please ask TI's engineers to help analyze the cause. Thank you