Part Number: DS90UB941AS-Q1

Other Parts Discussed in Thread: CDCEL913-Q1, CDCE913, LMK3H0102, CDCEL913

显示屏使用的是HV模式,941使用外部时钟,PCLK为180Mhz。据了解,941通过调整DE来实现外部时钟和DSI时钟同步。如果显示屏使用的是HV模式,是不是就会出现显示水波纹现象?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS90UB941AS-Q1

Other Parts Discussed in Thread: CDCEL913-Q1, CDCE913, LMK3H0102, CDCEL913

显示屏使用的是HV模式,941使用外部时钟,PCLK为180Mhz。据了解,941通过调整DE来实现外部时钟和DSI时钟同步。如果显示屏使用的是HV模式,是不是就会出现显示水波纹现象?

您好,是要根据显示屏是HV模式还是DE模式,来配置941和显示屏模式一致的,并且极性也需要一致。

出现水波纹我认为和这里的配置无关,如果模式不一致可能会出现显示异常,而不只是水波纹。

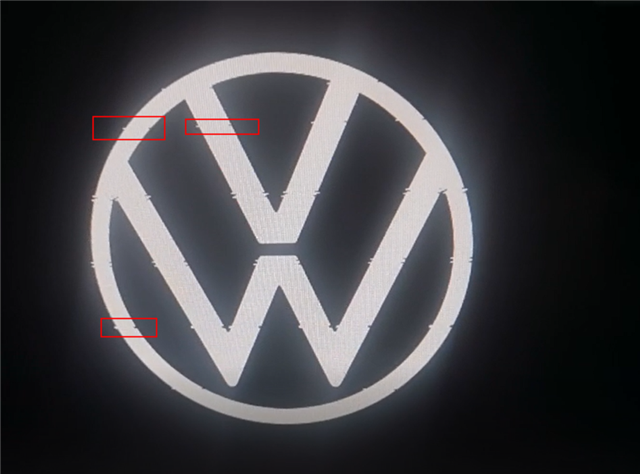

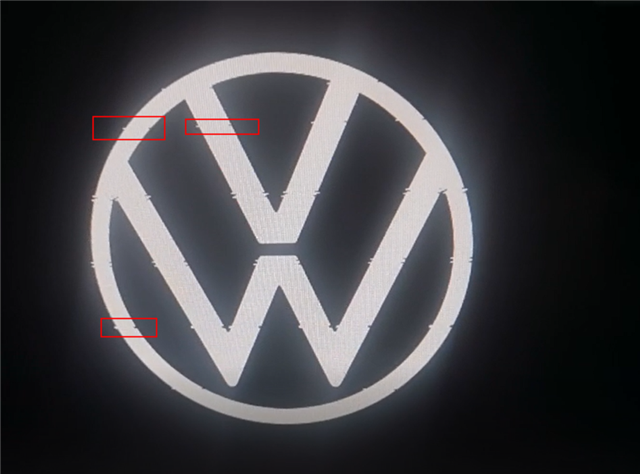

切换成913外部时钟,就会出现这种水波纹,有什么原因吗?对手件是948

只是切换成913的时钟,还是说913和948搭配使用?

913是ADAs系列,94x是IVI系列,两个系列的SER和DES是不兼容的哈, 不能搭配一起使用。

好的, 941使用DSI的时钟,显示是正常的,切换成913外部时钟,就会出现这种水波纹,那水波纹可以判断是时钟的原因。

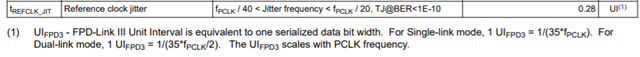

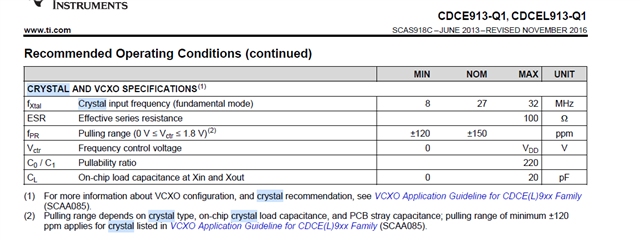

如果切换成外部时钟的话,那么外部时钟的jitter要求反而没有DSI clock 要求苛刻,但是也要满足datasheet中的jitter要求,如下:

关于DS90UB941 的DSI clock或external clock的jitter要求,可以看下资深工程师写的FAQ:

您好,我看了下CDCE913的数据手册,是可以提供外部时钟的。

我再看下这个问题,稍后给您答复。

现在使用的CDCEL913-Q1的jitter是可以满足180Mhz(88.8ps)的要求

180Mhz的像素时钟,941AS使用的是dual lane模式 ,我们可以计算下941的jitter要求。

Dual lane - (1/(35*180/2))*0.28 =88.8ps。

我认为问题可能时钟jitter这里的原因,不知您是如何测试的jitter,建议使用高速示波器的DPOJET程序来对 TJ@BER 做jitter分析。

941要求的jitter是针对total jitter 总抖动要求。

针对FPD link的器件,在测量total jitter的时候,可以看下这篇应用手册:

https://www.ti.com/lit/an/scaa120b/scaa120b.pdf

如果可以的话,可以使用和demo一样的时钟器件 LMK61E0M 来验证下。

Hi Kailyn

好的,我们测试一下total jitter。现在TI推荐LMK3H0102这颗时钟发生器,这颗的jitter比较小。

CDCEL913和LMK3H0102规格书中对外部时钟的jitter没有要求,这个是因为时钟发生器内部有去jitter的机制吗?

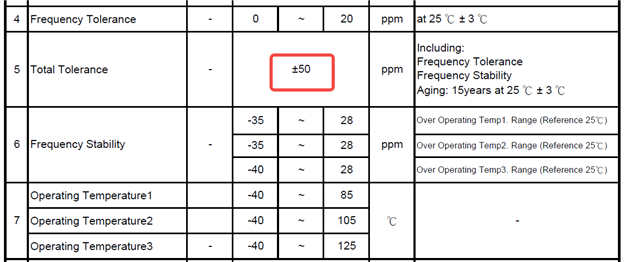

还是会根据负载端(941:88.8ps)要求选择晶振。是看晶振在25℃下的Frequency Tolerance

的频偏还是看Total Tolerance(over all)

我们913选择的晶振是TXC的AM25060307。

CDCEL913和LMK3H0102规格书中对外部时钟的jitter没有要求,这个是因为时钟发生器内部有去jitter的机制吗?

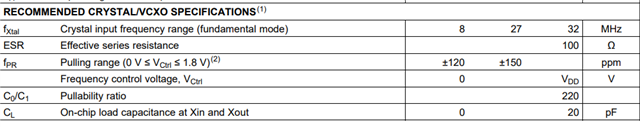

913对输入晶振或时钟的要求如下,没有明确要求输入jitter,但是jitter越低当然是越理想的。

内部没有集成jitter cleaner 的模块,但是集成了低噪声的PLL 内核。