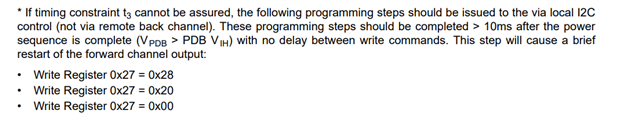

DS90UB933模组上电过程中I2C总线出现异常拉低,系统框图如下:

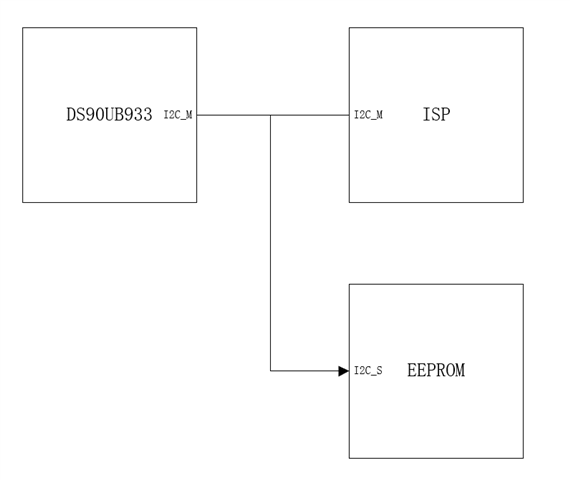

当整个模组上电时,电源建立完成后13ms左右,ISP开始读取EEPROM数据,但是当数据读到96 01 02 a0时(此时时间约为13.9ms左右)a0的bit[5]会被拉低,导致变成96 01 02 80。波形如下图:

这个问题并不是每次都能复现,是在模组启停车测试过程中概率性出现的,概率大约千分之二左右。

问题如下:

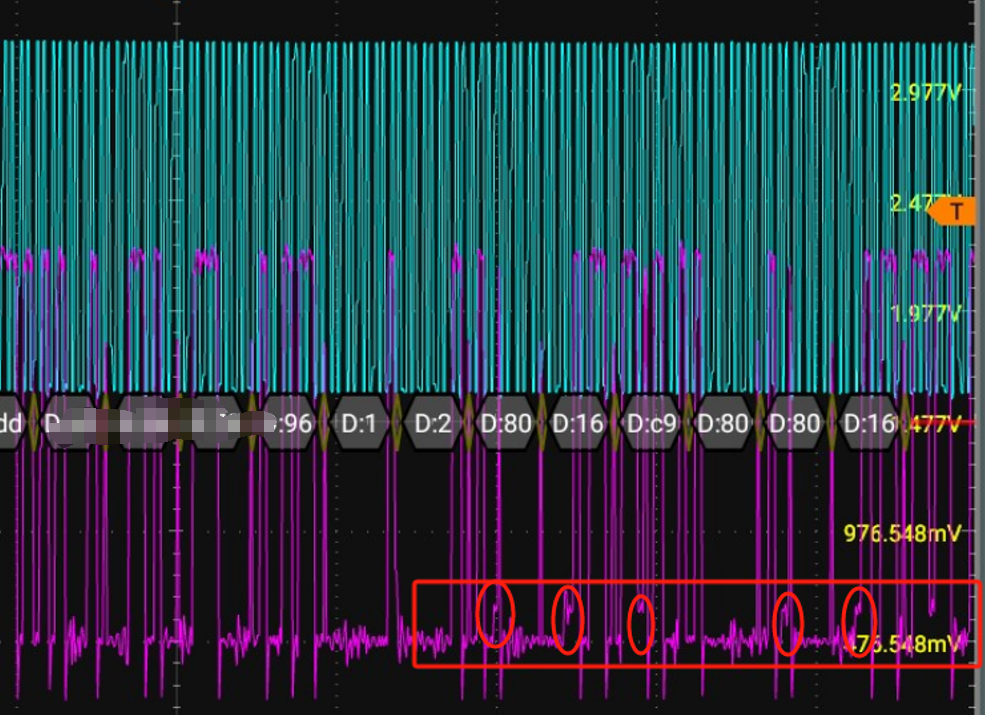

1、DS90UB933在上电过程中I2C接口是否会在Master到slave之间切换?如有切换,具体流程是怎么样的?

2、DS90UB933是否会干扰系统启动时ISP对EEPROM的读操作?