问题现象:

当SOC(927 LVDS输入端)设置为54Mhz时,CLK幅度为48mV左右,但是928 LVDS输出端 CLK幅度出现衰减24mV左右,与927输入信号不一致,

当我们把CLK频率降低为20Mhz时,927输入端与928输出端并不会出现衰减现象。

需求:

LVDS CLK信号传输一致,不出现衰减。

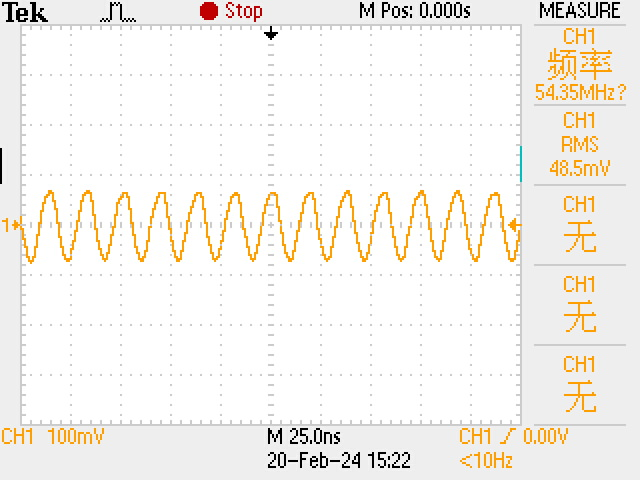

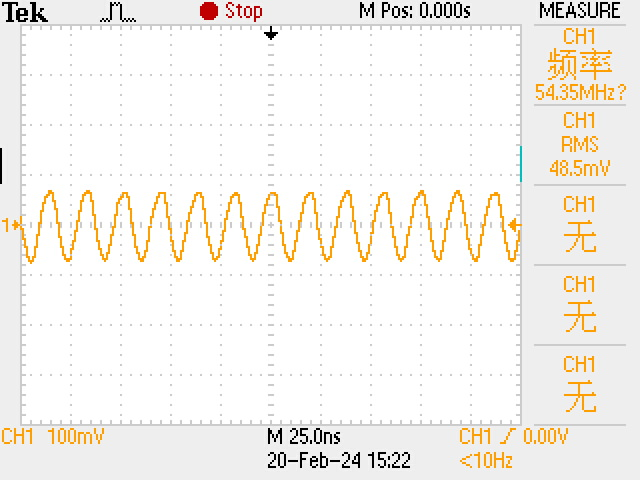

927 LVDS输入端附图:

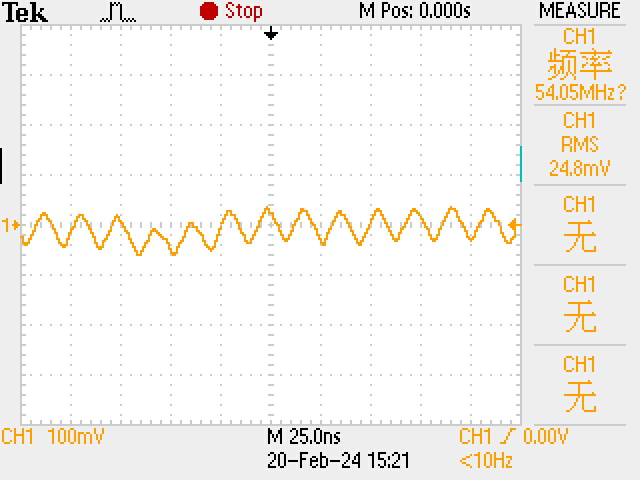

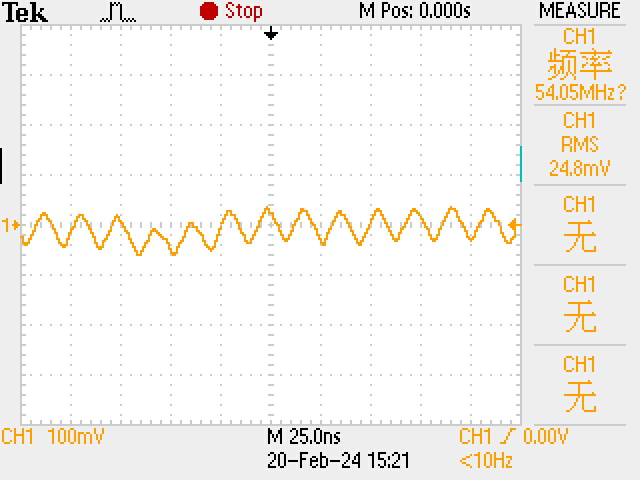

928 LVDS输出端附图:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

问题现象:

当SOC(927 LVDS输入端)设置为54Mhz时,CLK幅度为48mV左右,但是928 LVDS输出端 CLK幅度出现衰减24mV左右,与927输入信号不一致,

当我们把CLK频率降低为20Mhz时,927输入端与928输出端并不会出现衰减现象。

需求:

LVDS CLK信号传输一致,不出现衰减。

927 LVDS输入端附图:

928 LVDS输出端附图:

您好,第一张图是RxCLKIN 的差分信号Vid的波形还是RxCLKIN+或RxCLKIN-单端的波形?

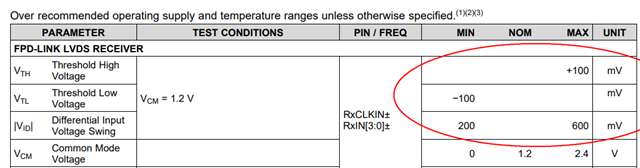

从波形和幅值来看,不满足1.2V共模电压,以及Vid的幅值范围要求:

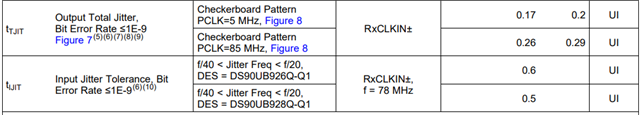

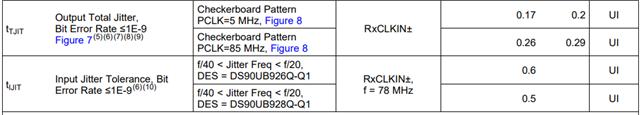

其次RXCLK的jitter要求对于FPD link整个link也是非常重要的,要测量下是否满足。

在满足输入要求的前提下,才能确保FPD link的正确传输。所以我建议是先确保输入时钟先满足927的输入要求。

从上面给的波形来看,输出波形不但幅值衰减同时也失真了。

但是对于Jitter,我们没有仪器去测量,我们也怀疑是这里的问题

第一张图是RxCLKIN+单端的波形,我们用示波器去测量的共模电压是大于1.2V,满足要求的

单端波形幅值为48mV的话,那么差分信号的幅值是单端信号的2倍,即96mV,并不满足Vid在200~600mV的幅值范围呢。

我们CLK设置为20MHz的时候,测到的差分信号的幅值为200mV,满足这个幅值范围

当我们把CLK频率降低为20Mhz时,927输入端与928输出端并不会出现衰减现象。

20Mhz的时候,幅值满足这个范围,所以和上述您提到的20Mhz的时候不会出现衰减相符,所以50Mhz的时候发生失真和衰减,可以排除是jitter的问题,应该是幅值不满足导致,您是否可以将50MHz的CLK满足幅值(而不是48mV)测试下?

54MHz的CLK时,最高峰峰值只能达到170mV,该如何去调整呢

您是Soc提供CLK输出给927作为输入是吗?

如果Soc的最高峰峰值只能达到170mV,是不满足最低200mV的要求的,所以则无法使用它给927 提供时钟。

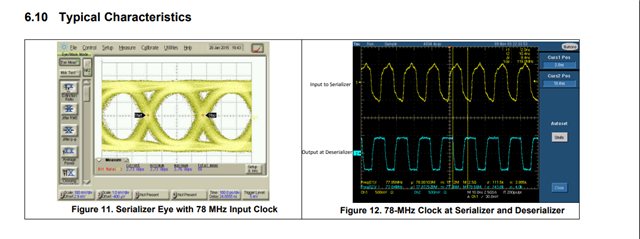

您好,您的这个时钟波形看起来有些失真。

这是78Mhz的差分输入时钟眼图,以及使用差分碳棒测试出来的输入到SER端和DES端输出的时钟波形。

我看您使用的示波器带宽是200Mhz,建议您使用高带宽的示波器再测试下,示波器测量信号相当于低频滤波器,如果带宽不够,高频信号会发生衰减,会噪声信号失真,幅值降低的现象。

您好,我想请问一下,927对 输入的 jitter的规格要求是哪个呢?

是0.2UI还是0.5UI呢?

您好,还有些问题需要请教您一下。

你们对Jitter测量的要求是什么?参数要设置什么,设备有什么要求吗?需要怎么去测量,要有什么测量的条件吗?

你们对Jitter测量的要求是什么?参数要设置什么,设备有什么要求吗?需要怎么去测量,要有什么测量的条件吗?

您好, 关于测量条件,以及测量方法,建议您将问题发布在E2E英文技术论坛上(https://e2e.ti.com/support/interface-group/interface/f/interface-forum),将由资深的英文论坛工程师为您提供帮助